Преобразуването на двоично в десетично може да се извърши с помощта на устройство, а именно декодер. Това устройство е един вид комбинационна логическа схема, която използва n-входните линии за генериране на 2n изходни линии. Тук изходът на това устройство може да е под 2n линии. Съществуват различни видове двоични декодери, които включват множество входове, както и множество изходи. Някои видове декодери включват един или повече активиращи входове заедно с входовете за данни. Винаги, когато входът за активиране е деактивиран, тогава всички изходи ще бъдат инактивирани. Въз основа на своята функция, двоичен декодер променя данните от n-входни сигнали към 2n изходни сигнали. При някои видове декодери те имат под 2n изходни линии. Така че в тази ситуация може да се повтори минимум един изходен прототип за различни входни стойности. Има два вида декодери от по-висок ред като декодер от 3 линии до 8 линии и декодер от 4 линии до 16 линии. Тази статия разглежда общ преглед на декодер от 3 до 8 реда.

Какво е декодер?

Декодерът е a комбинационна логическа схема който се използва за промяна на кода в набор от сигнали. Това е обратен процес на енкодер. Декодерната схема взема множество входове и дава множество изходи. Декодерна схема приема двоични данни от „n“ входове в уникален изход „2 ^ n“. В допълнение към входните щифтове, декодерът има щифт за активиране. Това позволява на щифта, когато е отрицателен, да направи веригата неактивна. в тази статия обсъждаме 3 до 8 реда декодер и демултиплексор.

По-долу е таблицата на истината за прост декодер от 1 до 2 линии, където A е входът, а D0 и D1 са изходите.

1 до 2 декодер

Схемата показва логиката на декодера от 1 до 2.

1 до 2 декодерна верига

Демултиплексорът е устройство, което взема един вход и дава една от няколкото изходни линии. Демултиплексърът взема по една единична входяща информация и след това избира един от отделните изходни линии един по един. Това е обратен процес на мултиплексор . Той също се нарича DEMUX или дистрибутор на данни. DEMUX преобразува входящата линия за последователни данни в изходни паралелни данни. DEMUX дава ‘2n’ изходи за ‘n’ линии за избор с един вход.

Demux

DEMUX се използва, когато веригата иска да изпрати сигнала за данни към едно от многото устройства. Декодер се използва за избор между много устройства, докато демултиплексор се използва за изпращане на сигнала към много устройства.

По-долу е таблицата на истината за 1 до 2 демултиплексора с „I“ като входни данни, D0 и D1 са изходните данни и A е линията за избор.

1 до 2 таблица на истината Demux

Схемата показва схемата на 1 до 2 демултиплексор.

1 до 2 Demux

Защо се нуждаем от декодер?

Основната функция на декодера е да промени кода в набор от сигнали, защото той е противоположен на енкодера, но проектирането на декодери е просто. Основната разлика между декодера и демултиплексора е комбинационна схема, която се използва, за да позволи само един вход, както и да го насочи към един от изходите, докато декодерът позволява няколко входа и генерира декодирания изход.

Стъпки за проектиране на декодер от 3 до 8 реда

Тук, декодер от 3 до 8 реда е декодер от по-висок ред, който е проектиран с два декодера от нисък ред, като декодери от 2 до 4 реда. Преди да приложим този декодер, ние проектирахме декодер от 2 до 4 реда.

Декодер от 2 до 4 линии

Този декодер от 2 до 4 реда включва два входа като A0 & A1 & 4 изхода като Y0 до Y4. Блоковата схема на този декодер е показана по-долу.

Декодер от 2 до 4 линии

Когато входовете и активирането са 1, тогава изходът ще бъде 1. Ето таблицата на истината за 2 до 4 декодера.

Е | А1 | A0 | Y3 | Y2 | Y1 | Y0 |

0 | х | х | 0 | 0 | 0 | 0 |

1 | 0 | 0 | 0 | 0 | 0 | 1 |

1 | 0 | 1 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 | 0 | 0 |

Булевият израз за всеки изход е

Y3 = E. A1. A0

Y2 = E. А1. A0 ′

Y1 = E. A1′. A0

Y0 = E. A1′. A0′

Всеки изход на този декодер включва един продуктов термин. Така че четирите продуктови термина могат да бъдат изпълнени чрез 4 AND порта, където всяка порта включва 3 входа, както и 2 инвертора. Логическата схема на декодера от 2 до 4 е показана по-долу. По този начин изходът на този декодер не е нищо друго освен минималните стойности на входовете и разрешаването е еквивалентно на 1. Ако разрешаването е нула, след това всички изходи на декодера ще бъдат еквивалентни на нула. По същия начин, декодер от 3 реда до 8 реда генерира осем minterms за 3 входни променливи от A0, A1 и A2.

Логическа диаграма от 2 до 4 декодера

Внедряване на декодер от 3 до 8 реда

Внедряването на този декодер от 3 реда до 8 реда може да се извърши с помощта на два декодера от 2 реда до 4 реда. По-горе обсъдихме, че декодерът от 2 до 4 линии включва два входа и четири изхода. И така, в 3 реда до 8-редов декодер, той включва три входа като A2, A1 и A0 и 8 изхода от Y7 - Y0.

Следната формула се използва за внедряване на декодери от по-висок ред с помощта на декодери от нисък ред

Необходимият брой декодери от по-нисък ред е m2 / m1

Където,

Броят на o / ps за декодера от по-нисък ред е ‘m1’

Броят на o / ps за декодера от по-висок ред е ‘m2’

Например, когато m1 = 4 & m2 = 8, тогава заменете тези стойности в горното уравнение. Можем да получим нужното не. на декодерите са 2. Така че, за прилагане на единичен декодер от 3 до 8, се нуждаем от два декодера от 2 реда до 4 реда. Тук блок-схемата е показана по-долу с помощта на два 2 до 4 декодера.

3 до 8 декодера с помощта на 2 до 4 линия

Паралелните входове като A2, A1 и A0 се дават на 3 реда до 8-редов декодер. Тук се дава комплимент на A3, за да се даде възможност на щифта на декодера да получи изходи като Y7 до Y0. Тези резултати са по-ниски 8 minterms. В горния декодер входът A3 е свързан, за да позволи на щифта да получи изходите от Y15 - Y8. И така, тези резултати са по-високите 8 minterms.

Декодер от 3 до 8 реда с помощта на Logic Gates

В 3 до 8 реда декодер, той включва три входа и осем изхода. Тук входовете са представени чрез A, B & C, докато изходите са представени чрез D0, D1, D2 ... D7.

Изборът на 8 изхода може да се направи въз основа на трите входа. И така, таблицата на истината на този декодер от 3 до 8 реда е показана по-долу. От следващата таблица на истината можем да забележим, че просто един от 8 изхода от DO - D7 може да бъде избран в зависимост от 3 избрани входа.

| ДА СЕ | Б. | ° С | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 |

0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

От горната таблица на истината от 3 реда до 8-редов декодер логическият израз може да бъде дефиниран като

D0 = A’B’C ’

D1 = A’B’C

D2 = A’BC ’

D3 = A’BC

D4 = AB’C ’

D5 = AB’C

D6 = ABC ’

D7 = ABC

От горните булеви изрази, изпълнението на 3 до 8 декодерна верига може да се извърши с помощта на три НЕ порта и 8-три входни И порта.

В горната схема трите входа могат да бъдат декодирани в 8 изхода, където всеки изход представлява един от междинните термини на трите входни променливи.

3-те инвертора в горната логическа схема ще осигурят допълнение към входовете и всяка една от портите И ще генерира една от междинните стойности.

Този вид декодер се използва главно за декодиране на всеки 3-битов код и генерира осем изхода, еквивалентни на 8 различни комбинации за входния код.

Този декодер е известен също като двоичен към осмичен декодер, тъй като входовете на този декодер представляват трибитови двоични числа, докато изходите представляват 8-те цифри в окталната числова система.

Блокова диаграма от 3 реда до 8 реда декодер

Тази схема на декодера дава 8 логически изхода за 3 входа и има щифт за разрешаване. Схемата е проектирана с логически порти AND и NAND. Отнема 3 двоични входа и активира един от осемте изхода. 3 до 8 линия декодер верига се нарича още двоичен към осмодесетичен декодер.

Блок-схема от 3 до 8 реда за декодер

Схемата на декодера работи само когато щифтът за активиране (E) е висок. S0, S1 и S2 са три различни входа и D0, D1, D2, D3. D4. D5. D6. D7 са осемте изхода. The логическа схема на 3 до 8 реда декодер е показано по-долу.

3 до 8 Декодерна верига

Декодер от 3 до 8 и таблица на истината

Таблицата по-долу дава таблицата на истината за 3 до 8 реда декодер.

| S0 | S1 | S2 | Е | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 |

| х | х | х | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Когато щифтът за активиране (E) е нисък, всички изходни щифтове са ниски.

1 до 8 Демултиплексор

ДА СЕ 1 ред до 8 реда демултиплексор има един вход, три избрани входни линии и осем изходни реда. Той разпределя данните от един вход в 8 изходни реда в зависимост от избрания вход. Din са входните данни, S0, S1 и S2 са избрани входове, а Y0, Y1, Y2, Y3, Y4, Y5, Y6, Y7 са изходите.

1 до 8 DEMUX

Схемата на схемата от 1 до 8 demux е показана по-долу.

1 до 8 Demux верига

3 до 8 Декодер / Демултиплексор

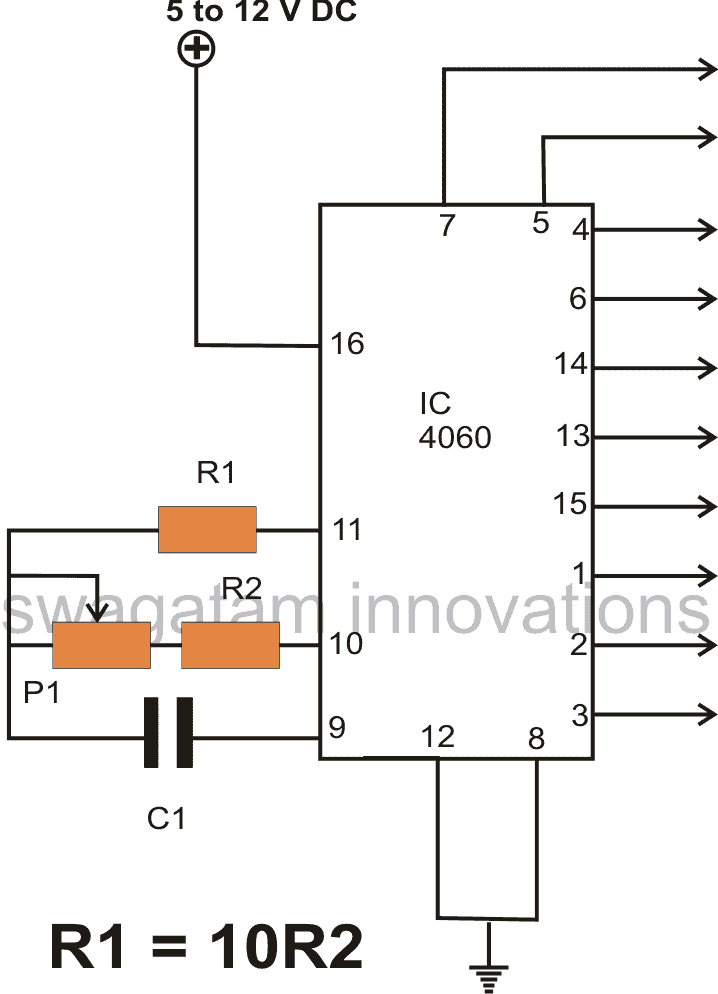

3 до 8 реда декодер IC 74HC238 се използва като декодер / демултиплексор. Демултиплексърът от 3 до 8 реда е комбинирана схема, която може да се използва както като декодер, така и като демултиплексор. IC 74HC238 декодира три двоични адресни входа (A0, A1, A2) в осем изхода (Y0 до Y7). Устройството има и три щифта Enable. Същата комбинация се използва като демултиплексор.

Конфигурация на ПИН

По-долу е дадена конфигурацията на щифтовете за декодера или демултиплекса IC74HC238 от 3 до 8 реда. Това е 16 пинов DIP.

Верига

Логическата схема обяснява работата на IC 74HC238.

Характеристики на 74HC238 IC

- Възможност за демултиплексиране

- Множество входове позволяват лесно разширяване

- Идеален за декодиране на избор на чип памет

- Активни ВИСОКИ взаимно изключващи се изходи

- Опция за множество пакети

Прилагане на декодер

- The Декодери са били използвани при аналогово-цифрово преобразуване в аналогови декодери.

- Използва се в електронни схеми за преобразуване на инструкции в управляващи сигнали на процесора.

- Те се използват предимно през логически вериги , трансфер на данни.

Приложения на Demultiplexer

- Използва се за свързване на един източник към множество дестинации.

- Demux се използва в комуникационните системи за пренасяне на множество сигнали от данни в една предавателна линия.

- Използва се в аритметични логически единици

- Използва се в серийни към паралелни преобразуватели при комуникация на данни.

Следователно това е основната информация за 3 до 8 линейни декодера и демултиплексори. Надявам се, че може да сте разбрали някои основни понятия по тази тема, като наблюдавате цифровите логически схеми и таблиците на истината и техните приложения. Освен това, всякакви съмнения относно тази статия или Последни проекти за електроника , Можете да напишете вашите виждания по тази тема в раздела за коментари по-долу.