The полеви транзистор (FET) е електронно устройство, в което електрическо поле се използва за регулиране на потока на тока. За да се осъществи това, се прилага потенциална разлика през изводите на портата и източника на устройството, което променя проводимостта между изтичането и изводите на източника, което води до преминаване на контролиран ток през тези изводи.

Извикват се FET еднополюсни транзистори тъй като те са проектирани да работят като устройства с един носител. Ще намерите различни видове транзистори с полеви ефект.

Символ

Графичните символи за n-каналните и p-каналните JFET могат да бъдат визуализирани на следващите фигури.

Можете ясно да забележите, че стрелките, които сочат навътре за n-каналното устройство, за да посочат посоката, в която IG(ток на затвора) трябва да тече, когато p-n кръстовището е пристрастено напред.

В случай на p-канално устройство условията са идентични, с изключение на разликата в посоката на символа на стрелката.

Разлика между FET и BJT

Полевият транзистор (FET) е тритерминално устройство, проектирано за широк спектър от приложения на веригата, които до голяма степен допълват тези на BJT транзистора.

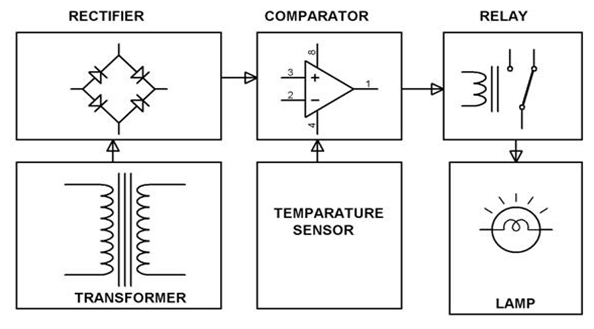

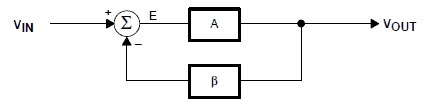

Въпреки че ще откриете значителни отклонения между BJT и JFET, всъщност има няколко съвпадащи характеристики, за които ще стане дума в следващите дискусии. Основната разлика между тези устройства е, че BJT е устройство, управлявано от ток, както е показано на фиг. 5.1а, докато транзисторът JFET е устройство, управлявано от напрежение, както е показано на фиг. 5.1б.

Казано по-просто, сегашният аз° Сна фиг. 5.1а е непосредствена функция на нивото на IБ.. За FET токът I е функция от напрежението VGSдадени на входната верига, както е показано на фиг. 5.1b.

И в двата случая токът на изходната верига ще се управлява от параметър на входната верига. В една ситуация текущо ниво, а в друга приложено напрежение.

Подобно на npn и pnp за биполярни транзистори, ще намерите n-канални и p-канални полеви транзистори. Но трябва да помните, че транзисторът BJT е биполярно устройство, като префиксът би- показва, че нивото на проводимост е функция на два носителя на заряд, електрони и дупки.

FET от друга страна е a еднополюсно устройство това зависи единствено от проводимостта на електрона (n-канал) или дупка (p-канал).

Фразата „полеви ефект“ може да се обясни по следния начин: всички ние сме наясно със силата на постоянния магнит да привлича метални стружки към магнита без никакъв физически контакт. Съвсем по подобен начин вътре в FET се създава електрическо поле от съществуващите заряди, които влияят на проводимостта на изходната верига, без да имат пряк контакт между управляващите и контролираните величини. Вероятно една от най-важните характеристики на FET е неговият висок входен импеданс.

В диапазон от 1 до много стотин мегаома, той значително надминава нормалните диапазони на входното съпротивление на конфигурациите BJT, изключително важен атрибут при разработването на линейни модели усилватели за променлив ток.

BJT обаче носи по-голяма чувствителност към вариациите на входния сигнал. Това означава, че промяната в изходния ток обикновено е значително по-голяма за BJTs, отколкото FETs за същия размер на промяната на техните входни напрежения.

Поради това стандартните печалби от променливотоково напрежение за BJT усилвателите могат да бъдат много по-високи в сравнение с FET.

Най-общо казано, полевите транзистори са значително по-устойчиви на топлина от BJT, а също така често са с по-малки размери по структура в сравнение с BJT, което ги прави специално подходящи за вграждане като интегрална схема (I° С)чипс.

Структурните характеристики на някои полеви транзистори, от друга страна, могат да им позволят да бъдат изключително чувствителни към физически контакти, отколкото BJT.

Още BJT / JFET връзка

- За BJT VБЪДА= 0,7 V е важният фактор за започване на анализ на неговата конфигурация.

- По същия начин параметърът IG= 0 A обикновено е първото нещо, което се има предвид при анализа на JFET верига.

- За конфигурацията на BJT IБ.често е първият фактор, който се налага да бъде определен.

- По същия начин за JFET обикновено е VGS.

В тази статия ще се съсредоточим върху JFET или транзистори с полево въздействие, а в следващата статия ще разгледаме транзистора с полеви ефект на метала-оксид-полупроводник или MOS-FET.

СТРОИТЕЛСТВО И ХАРАКТЕРИСТИКИ НА JFET

Както научихме Earliet, JFET има 3 потенциални клиенти. Един от тях контролира текущия поток между другите два.

Подобно на BJT, и в JFET устройствата n-каналното устройство се използва по-видно от p-каналните аналози, тъй като n устройства са склонни да бъдат по-ефективни и удобни за потребителя в сравнение с p-устройството.

На следващата фигура можем да видим основната структура или конструкция на n-канален JFET. Можем да видим, че съставът от n-тип образува основния канал през слоевете от тип p.

Горната част на канала от n-тип се свързва чрез омичен контакт с терминал, наречен дренаж (D), докато долната секция на същия канал също се свързва чрез омически контакт с друг терминал, наречен източник (S).

Двойката материали от тип p са свързани заедно с терминала, посочен като порта (G). По същество откриваме, че изводните и изходните терминали са свързани към краищата на n-тип канала. Терминалът на порта е свързан към двойка p-канален материал.

Когато няма напрежение, приложено към jfet, двата му p-n кръстовища са без никакви условия на отклонение. В тази ситуация съществува зона на изчерпване на всяко кръстовище, както е посочено на горната фигура, което изглежда доста като диоден p-n регион без отклонение.

Аналогия на водата

Работните и контролните операции на JFET могат да бъдат разбрани чрез следната аналогия с водата.

Тук налягането на водата може да бъде сравнено с приложената величина на напрежението от източване към източника.

Потокът на водата може да се сравни с потока на електроните. Устието на крана имитира изходния терминал на JFET, докато горната част на крана, където е принудена водата, изобразява изтичането на JFET.

Копчето за кран действа като Портата на JFET. С помощта на входен потенциал той контролира потока на електрони (заряд) от канализацията към източника, точно както копчето за кран контролира потока на водата през отвора на устата.

От структурата на JFET можем да видим, че изтичането и изходните клеми са в противоположните краища на n-канала и тъй като терминът се основава на електронния поток, можем да напишем:

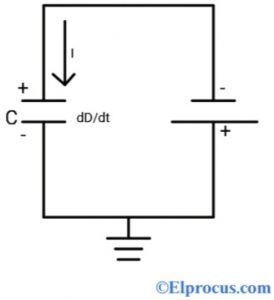

VGS= 0 V, VDSПоложителна стойност

На фигура 5.4 можем да видим положително напрежение VDSприложени през n-канала. Терминалът на порта е директно свързан към източника, за да се създаде условие VGS= 0V. Това позволява на портата и изходните терминали да бъдат с идентичен потенциал и води до изчерпване на долния край на всеки p-материал, точно както виждаме на първата диаграма по-горе с условие за непристрастие.

Веднага след като напрежение VДД(= VDS) се прилага, електроните се изтеглят към изтичащия терминал, генерирайки конвенционалния поток на ток ID, както е показано на фигура 5.4.

Посоката на потока на заряда разкрива, че изтичането и източникът на ток са равни по големина (Iд= АзС). Според условията, изобразени на фиг. 5.4, потокът на заряда изглежда доста неограничен и засегнат само от съпротивлението на n-канала между дренажа и източника.

Може да забележите, че регионът на изчерпване е по-голям около горната част на двата материала тип p. Тази разлика в размера на региона е идеално обяснена чрез фиг. 5.5. Нека си представим, че имаме еднакво съпротивление в n-канала, това може да бъде разделено до секциите, посочени на фиг. 5.5.

Настоящият аздможе да изгради диапазони на напрежението през канала, както е посочено на същата фигура. В резултат горната област на материала от типа p ще бъде обърната обратно с ниво от около 1,5 V, като долната област ще бъде просто обратна наклонена с 0,5 V.

Точката, че p-n кръстовището е обърнато по целия канал, води до ток на затвора с нулеви ампери, както е показано на същата фигура. Тази характеристика, която води до IG= 0 A е важна характеристика на JFET.

Както VDSпотенциалът се увеличава от 0 до няколко волта, токът се увеличава според закона на Ом и графиката на Iдред 5DSможе да изглежда доказано на фиг. 5.6.

Сравнителната правота на графиката показва, че за областите с ниска стойност на VDS, съпротивлението е основно равномерно. Както VDSсе издига и се приближава до ниво, известно като VP на фиг. 5.6, регионите на изчерпване се разширяват, както е дадено на фиг. 5.4.

Това води до видимо намаляване на ширината на канала. Намалената проводимост води до увеличаване на съпротивлението, пораждайки кривата на фиг. 5.6.

Колкото по-хоризонтална става кривата, толкова по-голямо е съпротивлението, което показва, че съпротивлението става към „безкрайни“ ома в хоризонталната област. Когато VDSсе увеличава до степен, при която изглежда, че двата региона на изчерпване могат да „контактуват”, както е показано на фиг. 5.7, поражда ситуация, известна като откъсване.

Сумата, с която VDSразвива тази ситуация се нарича щипка напрежение и то е символизирано от VPкакто е представено на фиг. 5.6. По принцип думата pinch-off е подвеждаща, тъй като предполага текущия Iдсе „отщипва“ и пада до 0 А. Както е доказано на фиг. 5.6, това едва ли изглежда очевидно в този случай. Аздзапазва ниво на насищане, характеризиращо се като IDSSна фиг. 5.6.

Истината е, че много малък канал продължава да съществува, с течение със значително висока концентрация.

Точката, в която идентификаторът не отпада щипка и запазва нивото на насищане, както е посочено на фиг. 5.6, се потвърждава със следното доказателство:

Тъй като няма изтичащ ток, елиминира възможността за различни потенциални нива чрез материала на n-канала за определяне на променящите се количества на обратното отклонение по p-n прехода. Крайният резултат е загуба на задействаното разпределение на региона на изчерпване щипка Да започнем с.

С увеличаването на VDSнад VP, регионът на близък контакт, където двата региона на изчерпване ще се срещнат един с друг, се увеличава по дължина по канала. Въпреки това нивото на ID продължава да бъде по същество непроменено.

По този начин моментът VDSе по-висока от Vстр, JFET придобива характеристиките на текущия източник.

Както е доказано на фиг. 5.8, токът в JFET се определя при Iд= АзDSS, но напрежение VDSпо-висока от VP се установява от свързания товар.

Изборът на IDSS нотация се основава на факта, че токът Drain to Source има късо съединение през портата към източника.

По-нататъшното разследване ни дава следната оценка:

АзDSSе най-високият изтичащ ток за JFET и се определя от условията VGS= 0 V и VDS> | VP |.

Забележете, че на фиг. 5.6 VGSе 0V за пълното разтягане на кривата. В следващите раздели ще научим как атрибутите на фиг. 5.6 се влияят като ниво на VGSе разнообразна.

VGS <0V

Волатирането, приложено през портата и източника, се означава като VGS, който е отговорен за контрола на JFET операциите.

Ако вземем примера на BJT, точно както кривите на I° Ссрещу VТОВАса определени за различни нива на IБ., подобно на кривите на Iдсрещу VDSза различни нива на VGSможе да бъде създаден за JFET аналог.

За това порталният терминал е настроен на продължителен по-нисък потенциал под нивото на потенциала на източника.

Позовавайки се на фиг. 5.9 по-долу, -1V се прилага през терминалите порта / източника за намалено VDSниво.

Целта на отрицателното потенциално пристрастие VGSе да се развият региони с изчерпване, наподобяващи ситуацията на VGS= 0, но при значително намалено VDS.

Това кара портата да достигне точка на насищане с по-ниски нива на VDSкакто е показано на фиг. 5.10 (VGS= -1V).

Съответното ниво на насищане за Iдможе да се установи, че е намален и всъщност просто продължава да намалява с VGSе направен по-негативен.

Можете ясно да видите на фиг. 5.10 как напрежението на откъсване продължава да пада с параболична форма като VGSстава все по-негативно.

И накрая, когато VGS= -Vстр, става достатъчно отрицателно, за да се установи ниво на насищане, което в крайна сметка е 0 mA. На това ниво JFET е напълно „изключен“.

Нивото на VGSкоето причинява Iдза достигане на 0 mA се характеризира с VGS= VP, където VPе отрицателно напрежение за n-канални устройства и положително напрежение за p-канални JFET.

Обикновено може да намерите повечето JFET таблици с данни, които се показват щипка напрежение, посочено като VGS (изключен)вместо VP.

Областта от дясната страна на локуса за откъсване на горната фигура е мястото, което обикновено се използва в линейни усилватели за постигане на сигнал без изкривяване. Този регион обикновено се нарича област с постоянен ток, насищане или линейно усилване.

Резистор с контролирано напрежение

Областта, която се намира от лявата страна на локуса за откъсване на същата фигура, се нарича омична област или контролирана от напрежението област на съпротивление.

В този регион устройството всъщност може да работи като променлив резистор (например в приложение за автоматично управление на усилването), като неговото съпротивление се контролира чрез приложения потенциал на порта / източника.

Можете да видите, че наклонът на всяка от кривите, което също означава съпротивлението на източване / източник на JFET за VDS

Тъй като правим VGS по-висок с отрицателен потенциал, наклонът на всяка крива става все по-хоризонтален, показвайки пропорционално нарастващи нива на съпротивление.

Ние можем да получим добро първоначално приближение до нивото на съпротивлението по отношение на VGS напрежението, чрез следното уравнение.

p-Channel JFET работи

Вътрешното оформление и конструкция на p-канален JFET е точно идентичен с n-каналния аналог, с изключение на това, че областите на p- и n-тип материали са обърнати, както е показано по-долу:

Посоките на текущия поток също могат да се разглеждат като обърнати, заедно с действителните полярности на напрежението VGS и VDS. В случай на p-канал JFET, каналът ще бъде ограничен в отговор на нарастващия положителен потенциал през портата / източника.

Нотацията с двоен индекс за VDSще доведе до отрицателно напрежение за VDS, както е показано на характеристиките на фиг. 5.12. Тук можете да намерите азDSSпри 6 mA, докато напрежението при изключване при VGS= +6V.

Моля, не се озадачавайте поради наличието на знак минус за VDS. Това просто показва, че източникът носи по-голям потенциал от канализацията.

Виждате, че кривите за високо VDSнивата рязко се повишават до стойности, които изглеждат неограничени. Посоченото покачване, което е вертикално, символизира ситуация на повреда, което означава, че токът през устройството на канала се контролира изцяло от външната схема в този момент от времето.

Въпреки че това не е очевидно на фиг. 5.10 за n-канално устройство, това може да е възможно при достатъчно високо напрежение.

Този регион може да бъде елиминиран, ако VDS (макс.)се отбелязва от листа с данни на устройството и устройството е конфигурирано така, че действителната VDSстойност е по-ниска от тази отбелязана стойност за всеки VGS.

Предишна: 5 най-добри проучени вериги за усилвател с мощност 40 вата Напред: 2N3055 Лист с данни, Pinout, Вериги на приложения