Тук изучаваме проста моностабилна схема, базирана на IC 555, чиято изходна моностабилна продължителност на времето започва само след освобождаване на входящия спусък, като по този начин се уверяваме, че продължителността на времето за включване на тригера се добавя с предварително програмираната продължителност на времето на включване на моностабила. Идеята е поискана от г-н Джон Броган

Технически спецификации

Бих искал да знам дали бих могъл да ви наема за много прост проект. Това е, за да ми помогне да науча схеми.

Търся следния тип верига (виж по-долу). Бихте ли ми казали какво би струвало проектирането?

Ще има 4 щифта на платката. 2 щифта от лявата страна на дъската, 2 щифта отдясно.

Когато някой затвори веригата на ЛЯВАТА страна на платката, или за миг, или колкото и дълго да държи веригата затворена, щифтовете от ДЯСНАТА страна на платката се затварят * PLUS * 2 минути след времето, когато веригата от ЛЯВАТА страна на дъската се отваря. (това е частта, в която съм затънал - как да направя веригата да остане затворена за „n“ минути след момента, в който е отворена друга верига.

Моля, уведомете ме какво бихте таксували, за да направите диаграма и избройте частите, които трябва да купя, за да направя това.

Благодаря ти!

Джон Броган

Колорадо

Дизайнът

С други думи, горната заявка изисква моностабилност, чийто изход при закъснение на състоянието ще се инициира само след освобождаване на входящия спусък, което означава, че да предположим, че моностабилният е проектиран да създава закъснение от 2 минути и нека приемем, че времето на задържане на входния тригер е x минути, общото закъснение на изходния pin3 на IC трябва да бъде = 2 минути + 'x' минути.

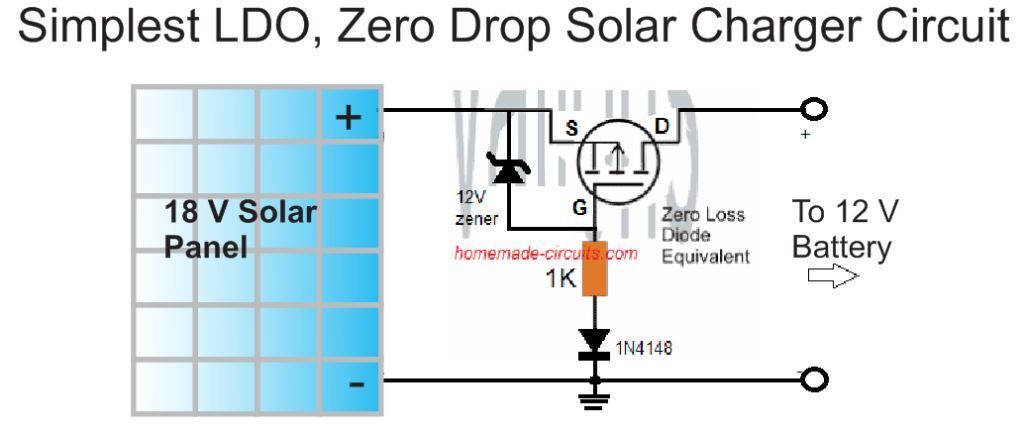

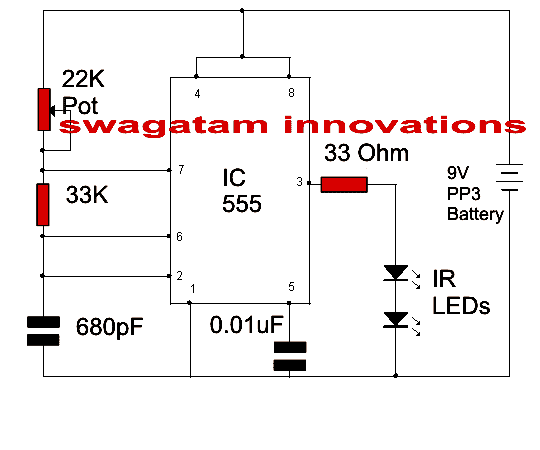

Дизайнът може просто да бъде конфигуриран чрез добавяне на PNP етап към стандартна моностабилна схема IC 555.

Позовавайки се на фигурата по-долу, виждаме стандартна моностабилна схема IC 555, която произвежда висока мощност за забавяне във времето, определено от R2 и C1. Това се инициира всеки път, когато pin2 е заземен за момент или може да е за някакъв относително по-дълъг период от време.

Но обикновено това би се случило веднага щом pin2 бъде заземен, без да се отчита продължителността на включване на спусъка и ние не искаме тази ситуация за предложения дизайн.

Проблемът е ефективно отстранен чрез включването на PNP устройството T1 в показаното положение на веригата.

Както се предлага в заявката, когато левите щифтове са затворени, T1 е разрешен с отрицателно отклонение, което го принуждава да провежда.

Горното условие позволява изходът да се покачи високо, но скъсява синхронизиращия кондензатор C1 чрез T1 емитер / cpllector, така че той не може да се зарежда, докато левите щифтове не бъдат отворени от потребителя.

След като се освободят левите щифтове, C1 има право да зарежда и инициира моностабилната операция за броене, при което релето задейства и затваря десните щифтове за обща продължителност на зададените две минути плюс продължителността, за която входът е бил затворен.

Електрическа схема

IC 555 спецификации на пиновете

Предишен: SMPS 2 x 50V 350W схема за аудио усилватели Напред: Двойна схема за превключване на реле за климатик