В тази публикация ще научим как да създаваме логически модули NOT, AND, NAND, OR и NOR, използвайки дискретни транзистори. Основното предимство на използването на транзисторни логически портове е, че те могат да работят дори при напрежения до 1,5 V.

В някои електронни приложения наличното напрежение може да е недостатъчно за захранване на TTL или дори CMOS IC. Това важи особено за джаджи, които работят на батерии. Без съмнение, винаги имате опцията за 3-волтова логическа IC. Те обаче не винаги са лесно достъпни за ентусиаста или експериментатора и не работят под техните определени спецификации за напрежение (обикновено под 2,5 волта DC).

Освен това може да има място само за една 1,5-волтова батерия в приложение, захранвано от батерии. Е, тогава какво ще правиш? Обикновено IC логически портове могат да бъдат заменени от транзисторизирани логически порти. За всяка конкретна логическа порта обикновено са необходими само няколко транзистора, а за типична инверторна логика на NOT gate е необходим само един транзистор.

FETs срещу биполярен транзистор

Транзистори с полеви ефекти (FET) срещу биполярни транзистори : кой е по-добрият вариант за логически схеми с ниско напрежение? Една страхотна характеристика на ФАКТИ е, че тяхното 'включено' съпротивление е невероятно ниско. Освен това те се нуждаят от много нисък ток на включване на вратата.

Те обаче имат едно ограничение при приложения с изключително ниско напрежение. Обикновено границата на напрежението на портата е около един волт. Освен това, наличното напрежение може да намалее под оптималния работен обхват на FET, ако към портата е прикрепен резистор за ограничаване на тока или съпротивление надолу.

Обратно, биполярните превключващи транзистори имат предимство при изключително ниско напрежение, приложения с една батерия, тъй като се нуждаят само от 0,6 до 0,7 волта, за да се включат.

Освен това, по-голямата част от обичайните FETs, които обикновено се продават в мехурчета в най-близкия магазин за електроника, често са по-скъпи от биполярните транзистори. Също така, голям пакет от биполярни транзистори обикновено може да бъде закупен на цената на чифт FET транзистори.

Работата с FET изисква значително повече внимание, отколкото обработката на биполярни транзистори. Електростатичната и общата експериментална злоупотреба правят FET особено податливи на повреда. Изгорелите компоненти могат да съсипят една приятна, творческа вечер на експерименти или иновации, да не забравяме емоционалната болка от отстраняването на грешки.

Основи на превключващите транзистори

Примерите за логически схеми, обяснени в тази статия, използват биполярни NPN транзистори, тъй като те са достъпни и не се нуждаят от специална обработка. За да избегнете повреда на устройството или частите, които го поддържат, трябва да се вземат подходящи мерки за безопасност, преди да свържете вашата верига.

Въпреки че нашите схеми са съсредоточени предимно върху биполярни съединителни транзистори (BJT), те биха могли еднакво добре да бъдат конструирани с помощта на FET технология.

Основната верига на превключвателя е просто транзисторно приложение, което е един от най-лесните дизайни.

Създаване на NOT Gate с единичен транзистор

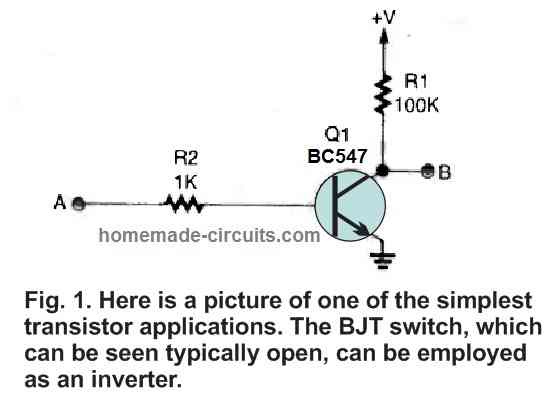

Схема на транзисторния превключвател е показана на Фигура 1. В зависимост от това как е реализиран в конкретно приложение, превключвателят може да се разглежда или като поддържан на ниско ниво, или като нормално отворен.

Един прост инверторен логически порт NOT gate може да бъде създаден от директната превключваща верига, показана на фиг. 1 (където точка A е входът). NOT gate работи по такъв начин, че ако към базата на транзистора (точка A; Q1) не се осигури постоянно напрежение, той ще остане изключен, което води до високо или логическо 1 (равно на V+ ниво) на изхода ( точка Б).

Въпреки това, транзисторът се активира, когато се осигури правилното отклонение към основата на Q1, избутвайки изхода на веригата ниско или до логическа 0 (почти равно на нулев потенциал). Транзисторът, означен като Q1, е биполярен транзистор с общо предназначение или BC547, който обикновено се използва в комутационни и усилвателни приложения с ниска мощност.

Всеки транзистор, който е еквивалентен на него (като 2N2222, 2N4401 и т.н.), ще работи. Стойностите на R1 и R2 бяха избрани, за да се постигне компромис между ниска консумация на ток и съвместимост. Във всички конструкции всички резистори са 1/4 вата, 5% единици.

Захранващото напрежение се регулира между 1,4 и 6 волта DC. Имайте предвид, че веригата може да работи като буфер, когато товарният резистор и изходната връзка са изместени към емитера на транзистора.

Създаване на буферна врата с помощта на единичен BC547 BJT

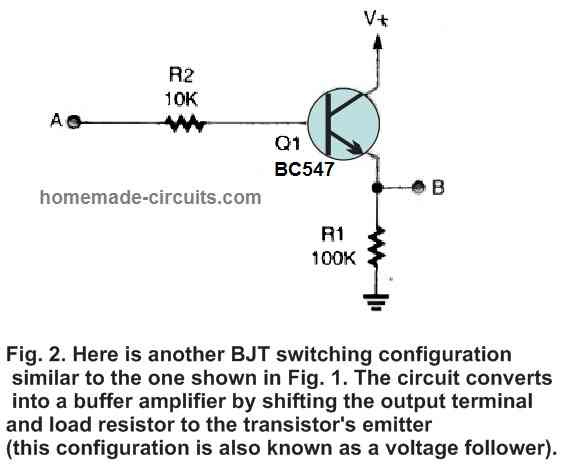

Повторител на напрежението или буферен усилвател е вид конфигурация на логическо превключване, идентична на тази, показана на фигура 2. Трябва да се отбележи, че товарният резистор и изходният терминал са изместени от колектора на транзистора към неговия емитер в тази верига, което е основната разлика между този дизайн и този, показан на фиг. 1.

Функционирането на транзистора може също да бъде 'обърнато' чрез преместване на товарния резистор и изходния терминал към другия край на BJT.

С други думи, когато към входа на веригата не се предоставя отклонение, изходът на веригата остава нисък; обаче, когато към входа на веригата се подаде отклонение с подходящо напрежение, изходът на веригата става висок. (Това е точно обратното на това, което се случва в по-ранната верига.)

Проектиране на логически вентили с два входа с помощта на транзистори

И порта, използваща два транзистора

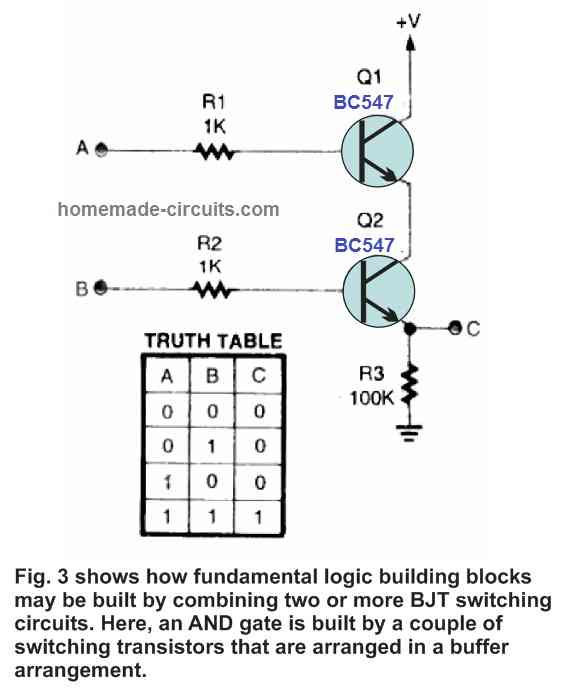

Фигура 3 илюстрира как може да се създаде основен И порт с два входа с помощта на двойка буфери, заедно с таблицата на истината за този портал. Таблицата на истината илюстрира какви биха били изходните резултати за всеки отделен набор от входове. Точки A и B се използват като входове на веригата, а точка C служи като изход на веригата.

Важно е да се отбележи от таблицата на истината, че само един набор от входни параметри води до логически висок изходен сигнал, докато всички други входни комбинации водят до логически нисък изход. Изходът на И портата на фигура 3 остава малко под V+, след като стане висок.

Това се случва поради спада на напрежението между двата транзистора (Q1 и Q2).

NAND Gate, използващ два транзистора

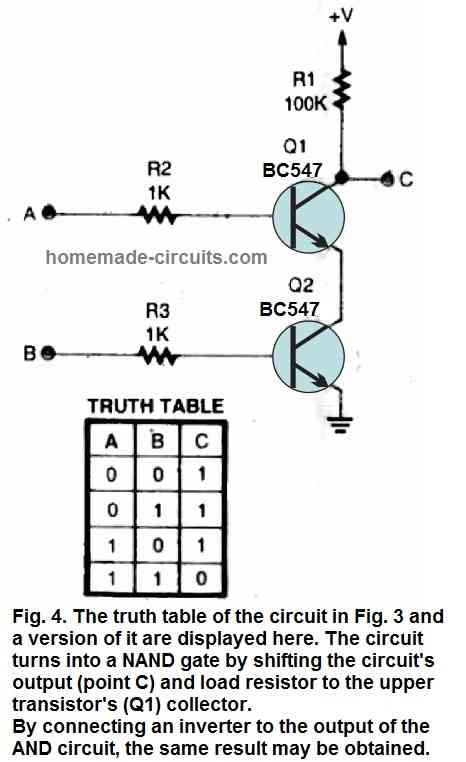

Друг вариант на веригата на Фигура 3 и свързаната таблица на истината са показани на Фигура 4. Веригата се превръща в NAND порта чрез изместване на изхода (точка C) и изходния резистор към колектора на горния транзистор (Q1).

Тъй като Q1 и Q2 трябва да бъдат включени, за да изтеглят ниската страна на R1 към земята, загубата на напрежение на изход C е незначителна.

Ако транзисторните И или транзисторните NAND гейтове се нуждаят от повече от два входа, повече транзистори биха могли да бъдат свързани в показаните конструкции, за да осигурят три, четири и т.н. входни И или NAND гейта.

Въпреки това, за да се компенсират загубите на напрежение на отделните транзистори, V+ трябва да се увеличи съответно.

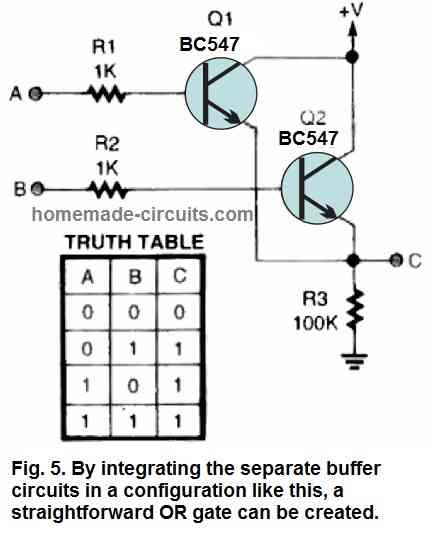

ИЛИ порта с два транзистора

Друга форма на логическа схема с два входа може да се види на фигура 5, заедно с таблицата на истината на веригата OR-gate.

Изходът на веригата е висок, когато или вход A, или вход B са натиснати високо, но поради каскадните транзистори спадът на напрежението е над 0,5 волта. И отново, показаните цифри показват, че има достатъчно напрежение и ток за работа на последващия транзисторен гейт.

NOR Gate, използващ два транзистора

Фигура 6 изобразява следващия порт в нашия списък, NOR порт с два входа, заедно с неговата таблица на истината. Подобно на това как AND и NAND портите реагират един на друг, ИЛИ и НЕ веригите правят същото.

Всеки от показаните гейтове е в състояние да достави достатъчно задвижване, за да активира поне един или повече съседни транзисторни гейтове.

Приложения на транзисторен логически порт

Какво правите с обяснените по-горе цифрови схеми, които сега притежавате? Всичко, което бихте могли да постигнете с конвенционалните TTL или CMOS гейтове, но без да се притеснявате за ограниченията на захранващото напрежение. Ето няколко приложения на транзисторно-логически портове в действие.

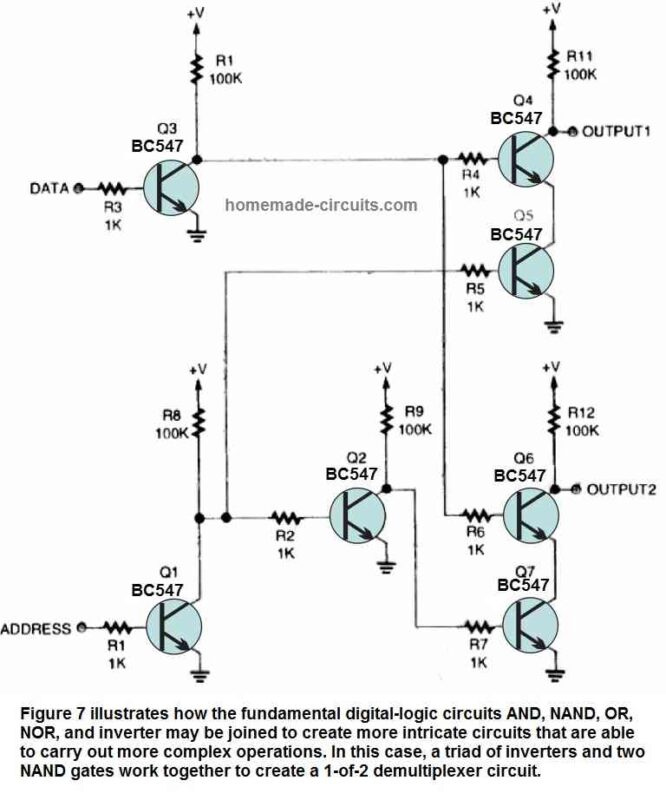

Демултиплексорна верига

1-от-2 демултиплексор с три NOT gate и две NAND вериги се вижда на Фигура 7. Подходящият изход се избира с помощта на еднобитовия 'адресен вход', който може да бъде OUTPUT1 или OUTPUT2, докато се прилага управляващата информация към веригата, използвайки входа DATA.

Веригата работи най-ефективно, когато скоростта на данни се поддържа под 10 kHz. Функционалността на веригата е проста. Входът DATA се захранва с необходимия сигнал, който включва Q3 и инвертира входящите данни в колектора на Q3.

Изходът на Q1 се управлява високо, ако входът ADDRESS е нисък (заземен или не се предоставя сигнал). В колектора на Q1 високият изход се разделя на два пътя. В първия път изходът на Q1 се подава към основата на Q5 (един от краката на NAND порта с два входа), като го включва и следователно 'активира' NAND порта, съставен от Q4 и Q5.

Във втория път високият изход на Q1 се подава едновременно на входа на друг НЕ порт (Q2). След преминаване през двойна инверсия, продукцията на Q2 става ниска. Този нисък ток се захранва от базата на Q7 (един терминал на втори NAND гейт, съставен от Q6 и Q7), като по този начин се изключва веригата NAND.

Всяка информация или сигнал, приложен към входа DATA, пристига на OUTPUT1 при тези обстоятелства. Алтернативно, ситуацията е обратна, ако на входа ADDRESS се подаде висок сигнал. Това означава, че всяка информация, предоставена на веригата, ще се покаже на OUTPUT2, тъй като портата Q4/Q5 NAND е деактивирана, а вратата Q6/Q7 NAND е активирана.

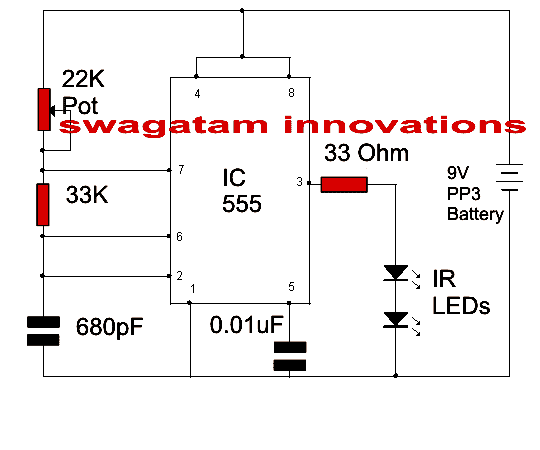

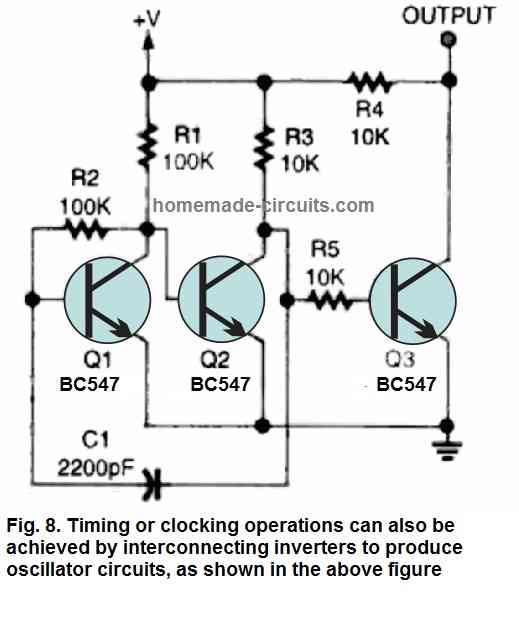

Осцилаторна верига (тактов генератор)

Следващото ни приложение за транзисторен логически гейт, илюстрирано на фиг. 8, е основен тактов генератор (известен също като осцилатор), направен от три обикновени НЕ гейт инвертора (единият от които е предубеден, използвайки резистор за обратна връзка, R2, който го поставя в аналоговата област).

За да се компенсира изхода, е включен трети NOT гейт (Q3), който доставя допълнение към изхода на осцилатора. Стойността C1 може да бъде увеличена или намалена, за да се промени работната честота на веригата. Изходната форма на вълната има честота от около 7 kHz с V+ при 1,5 волта DC, като се използват посочените стойности на компонента.

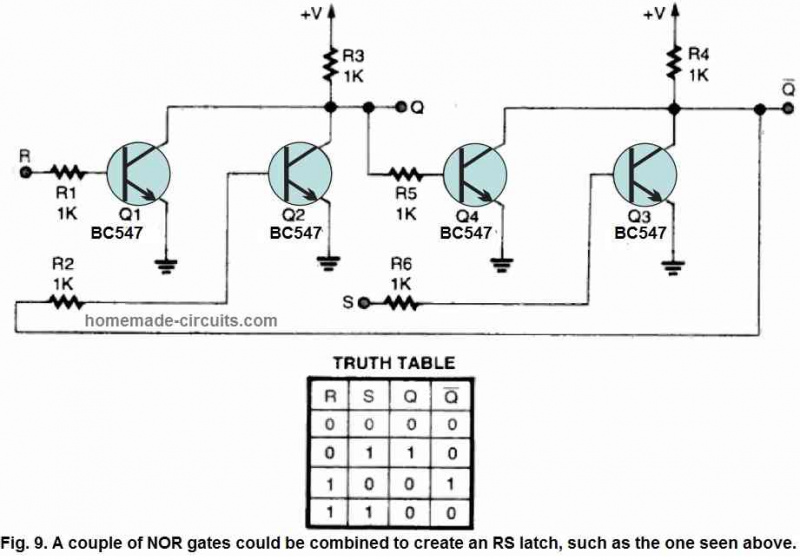

RS заключваща верига

Фигура 9 показва нашата последна схема на приложение, RS резе, съставено от два NOR порта. За да се осигури здравословно изходно задвижване на изходите Q и Q, резисторите R3 и R4 се настройват на 1k ома.

Истинната таблица на RS резето се показва заедно със схематичния дизайн. Това са само няколко илюстрации на няколко надеждни, нисковолтови, цифрови вериги с логическа врата, които могат да бъдат създадени с помощта на отделни транзистори.

Схемите, използващи транзистирана логика, се нуждаят от твърде много части

Много проблеми могат да бъдат решени с помощта на всички тези нисковолтови транзисторни логически схеми. Въпреки това, използването на твърде много от тези транзисторни порти може да доведе до нови проблеми.

Броят на транзисторите и резисторите може да стане доста голям, ако приложението, което създавате, съдържа голямо количество порти, заемащи ценно пространство.

Използването на транзисторни масиви (много транзистори, затворени в пластмаса) и SIP (Single Inline Package) резистори вместо отделни единици е един от начините за решаване на този проблем.

Горният подход може да спести един тон пространство на печатна платка, като същевременно поддържа производителност, равна на тази на техните пълноразмерни еквиваленти. Транзисторните матрици се предлагат в опаковки за повърхностен монтаж, 14-щифтови проходни отвори и четири пакети.

За повечето вериги типовете смесващи транзистори може да са доста приемливи.

Независимо от това, препоръчително е експериментаторът да работи с един тип транзистор за изграждане на транзисторизираните логически схеми (което означава, че ако създадете част от порта, използвайки BC547, след това се опитайте да използвате същия BJT, за да направите и останалите останали порти).

Причината е, че различните варианти на транзистори могат да имат малко по-различни свойства и следователно могат да се държат по различен начин.

Например, за някои транзистори основната граница на включване може да е по-голяма или по-малка от друга, или може да има общо усилване на тока, което е малко по-високо или по-ниско.

От друга страна, цената за закупуване на пакетна кутия от един тип транзистор също може да бъде по-ниска. Производителността на вашите схеми ще се подобри, ако вашите логически портове са изградени с помощта на съвпадащи транзистори и проектът като цяло ще бъде по-възнаграждаващ в крайна сметка.