Терминът VLSI означава „Многомащабна интеграционна технология“, която включва проектиране на интегрални схеми (ИС) чрез комбиниране на хиляди транзистори логично в един чип от различни логически схеми . Тези интегрални схеми в крайна сметка намаляват заетото пространство на веригата в сравнение с веригите с конвенционалните интегрални схеми. Изчислителната мощност и използването на пространството са основните предизвикателства на дизайна на VLSI. Прилагането на проекти за VLSI отваря предизвикателна и светла кариера както за студенти, така и за изследователи. Някои от новите тенденции в областта на VLSI са Програмируем масив на портала приложения (FPGA), ASIC проекти и SOC. Списък на някои от VLSI проектите е даден по-долу за тези студенти, които искрено търсят проекти в тази област. Тази статия разглежда общ преглед на VLSI проекти, базирани на FPGA, Xilinx, IEEE, Mini, Matlab и др., Изброени по-долу. Тези проекти са много полезни за студенти по инженерни науки, студенти по M.tech.

VLSI проекти за студенти по инженерство

VLSI проекти с резюмета за студенти по електронен инженер са разгледани по-долу.

VLSI проекти

1). Трансформация на дискретна вълна, базирана на 3D повдигане

Този проект помага за осигуряването на високо прецизни изображения, като използва кодирането на изображение, без да губи данните си. За да се постигне това, този процес реализира повдигащ филтър в зависимост от преобразуването на 3D дискретна архитектура на VLSI с вейвлет.

2). Проектиране на SFQ множител с 4-битов с ефективно чрез високоскоростен хардуер

Този проект се използва главно за внедряване на модифициран енкодер на щанд (MBE) с 4-битов SFQ базиран множител . Този множител осигурява добра производителност в сравнение с конвенционалния енкодер на кабината. Този проект се използва главно в приложенията с критично забавяне.

3). Криптографски процесор, използван в смарт карти с ефективна площ

Този проект се използва за реализиране на три криптографски алгоритма, поддържани както от частни, така и от публични ключове, използвани в Смарт карта приложения за осигуряване на изключително защитена проверка и данни на потребителите комуникация .

4). Умножител с висока скорост или ниска мощност с фалшив метод за потискане на мощността

Тази предложена система филтрира безполезните фалшиви сигнали на аритметичните единици, за да се избегне ненужното предаване на данни, което не влияе на последните изчислителни резултати. Тази система използва SPST метод за множители за постигане на ниска мощност и високоскоростно предаване на данни.

5). Компресия и декомпресия на алгоритъм без данни без загуби

Този проект се реализира главно за двустепенна хардуерна архитектура в зависимост от характеристиката на алгоритъма PDLZW (Parallel Dictionary LZW), както и алгоритъма на Adaptive Huffman тип, който се използва както за приложенията на компресиране на данни без загуби и декомпресия без загуби.

6). Архитектурата на Turbo Decoder с ниска сложност за енергийно ефективни WSN

Предложената система се използва за намаляване на общото потребление на енергия по време на предаване на данни на WSN чрез алгоритъма за разлагане на LUT-Log-BCJR към основните операции на ACS (Add Compare Select).

7). VLSI архитектура за ефективно премахване на импулсен шум на изображение

Тази предложена система се използва главно за подобряване на качеството на изображението визуално, за да се избегнат шансовете да бъдат повредени с импулсен шум, за да се приложи ефективна VLSI архитектура с помощта на филтър за запазване на ръба.

8). Архитектурата на процесор в памет, използван за компресиране на мултимедия

Тази предложена система осигурява архитектура с ниска сложност за a процесор в памет за поддръжка на мултимедийни приложения, а именно компресиране на изображения, видео чрез прилагане на огромна единична инструкция, множество концепции за данни и инструкция.

9). Техника за синхронизиране на синхронизирането със скорост на символи за безжични OFDM системи с ниска мощност

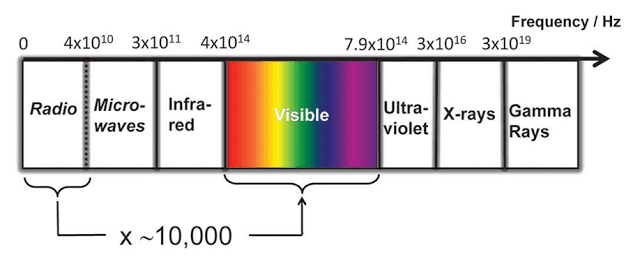

Тази предложена система се използва главно за подобряване на безжичния OFDM (Orthogonal Frequency Division Мултиплексиране ) система чрез намаляване на мощността на цялата основна лента с помощта на часовник генератор с регулируем фаза и динамичен контролер за синхронизиране на пробите.

10). Внедряване на акумулатор с ниска мощност и високоскоростен множител с SPST Adder & Verilog

Този проект се използва за проектиране на MAC с ниска мощност и висока скорост (умножител и акумулатор) чрез приемане на метода за фалшиво потискане на мощността на MBE (модифициран енкодер на кабината). Чрез използването на този дизайн може да се избегне разсейването на мощността на цялото превключване.

11). Проектиране и внедряване на роботизиран процесор чрез активиране на анти-сблъсък с RFID технология

Предложената система се използва главно за внедряване на робот-процесор с анти-сблъсък, за да се избегне физическият сблъсък на роботи в средата на много-робот. Този алгоритъм се реализира основно с помощта на VHDL и RFID технология.

12). Проектиране на логическа схема с енергийно ефективно използване на адиабатен метод

Тази система демонстрира логическия дизайн на схемата чрез ефективен адиабатичен метод в сравнение чрез конвенционален CMOS дизайн с помощта на схеми, използващи Порти NAND & NOR . Чрез използването на адиабатен метод, разсейването на мощността в мрежата може да бъде намалено, както и да рециклира съхранената енергия в товарния кондензатор.

3). Система за криптиране за повишаване на изчислителната скорост на системата

Основното намерение на този проект е да се подобри сигурността на предаването на данни, за да се подобри скоростта на изчисляване чрез внедряване на алгоритъма на AES с помощта на FPGA. Така че тази симулация, както и математическият дизайн, могат да се извършват с помощта на VHDL кода.

14). IP блок на AHM или разширена високопроизводителна шина

Този проект се използва главно за проектиране на архитектура на Advanced Микроконтролер Bus (AMB) с помощта на AHBN (Advanced High-Performance Bus). Този проект може да бъде проектиран с VHDL код чрез внедряване на блоковете като master & save.

15). Базиран на DSM многомодов RF приемо-предавател с многоканален

Тази система се използва главно за проектиране на многомодова архитектура на предавател и приемник и RF многоканал с модулатор Delta-Sigma. Тази предложена система използва VHDL език за реализиране на две архитектури.

16). Концентраторът на нокаут превключвател, използващ режим на асинхронен трансфер

Чрез използването на този проект може да се проектира нокаут ключ, базиран на асинхронен трансфер, с помощта на инструменти като VHS и VHDL. Този превключвател може да се използва в мрежите на виртуални верижни пакети, както и в приложенията на дейтаграмата.

17). Поведенчески синтез на асинхронни вериги

Този проект се използва главно за осигуряване на техника за поведенчески синтез, използвана за асинхронни вериги. И двата шаблона като balsa и асинхронните реализации са основните елементи в дизайна.

18). AMBA Дизайн, използващ съвместим контролер на паметта на AHB

Този проект се използва за проектиране на MC (контролер на паметта) в зависимост от AMBA (Advanced Microcontroller Bus Architecture) за управление на системната памет с помощта на основна памет като SRAM & ROM.

19). Внедряване на Adder Tree Adder

Носителят на дървесни носители, базиран на VLSI дизайн, се нарича най-добри сумиращи производителности, за разлика от обичайните двоични суматори. Сумарите, които са реализирани от този проект, са покриващо дърво, коге-камък и рядък коге-камък.

20). Въртене с фиксиран ъгъл на CORDIC дизайн

Основната концепция на тази предложена система е да завърта вектори с помощта на фиксирани ъгли. Тези ъгли са необходими за игри, роботика, обработка на изображение и т.н. Чрез използването на този проект може да се постигне векторно въртене чрез използване на специфични ъгли по дизайна на CORDIC (цифров компютър с координатно въртене).

21). Дизайн на FIR филтър с разпределена аритметика на таблицата за търсене

Тази предложена система главно подобрява FIR филтър изпълнение чрез проектиране с помощта на разпределена аритметика на триизмерна таблица за търсене на мястото на множителя. Така че този дизайн може да бъде реализиран с помощта на софтуер като FPGA и Xilinx.

22). Push-Pull импулсни резета с висока скорост и ниска мощност

Този проект се използва за изпълнение на енергийно ефективни и високоефективни импулсни резета, използвани главно за VLSI системи чрез използване на нова топология. Тъй като тази топология зависи главно от задвижването на последния етап с издърпване, използващо две разделителни ленти през генератор на условен импулс.

23). Аритметичен кодер VLSI архитектура в SPIHT

Тази предложена система подобрява производителността на метода за аритметично кодиране при компресиране на изображения в йерархични дървета (SPIHT) с високоскоростна архитектура в зависимост от FPGA.

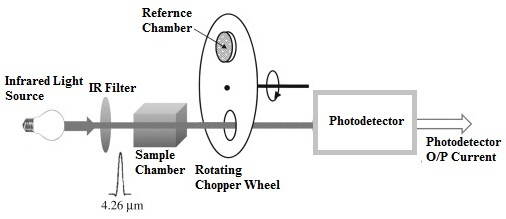

24). Потискане на шума на ЕКГ сигнал на базата на FPGA

Този проект се използва за овладяване на шума в рамките на ЕКГ сигнали чрез два средни филтъра със съответно 91 и 7 размера на пробните точки. Така че този процес може да бъде постигнат чрез прилагане на FPGA дизайн въз основа на VHDL код.

25). VLSI базиран високоефективен процесор за мащабиране на изображения с ниска цена

Този проект се използва за внедряване на алгоритъм за процесор за мащабиране на изображения, базиран на VLSI с по-малко памет и висока производителност. Предложеният системен дизайн съдържа предимно комбиниране на филтър, реконфигурируеми динамични методи и споделяне на хардуер за намаляване на разходите.

26). Ефективно проектиране и изпълнение на архитектурата на Systolic Array

Основната концепция на този проект е да се проектира хардуерен модел, използван за множителя на систоличния масив. Този масив може да се използва главно за изпълнение на двоично умножение с помощта на VHDL платформата. Предложеният системен дизайн може да бъде реализиран с помощта на софтуера FPGA & Isim.

27). QPSK Дизайн и синтез с използване на VHDL код

QPSK е един от основните методи за модулация. Този метод се използва в приложенията на сателитното радио. Тази техника на модулация може да бъде приложена чрез обратими логически портали. Проектирането на QPSK техниката може да се направи с помощта на VHDL кода.

28). Дизайн и внедряване на DDR SDRAM контролер с висока скорост

Предложената система се използва за проектиране на DDR SDRAM контролер за прехвърляне на данните за пакети в зависимост от високата скорост за синхронизиране на тези данни между веригата на вградената система и DDR SDRAM. Използвайки езика VHDL, кодът може да бъде разработен.

29). 32-битов RISC процесор Дизайн и внедряване

Основната концепция на този проект е да се внедри 32 бита RISC (Компютър с намален набор от инструкции) с помощта на инструмент като XILINK VIRTEX4. В този проект са проектирани 16 набора от инструкции, където всяка инструкция може да бъде изпълнена в един цикъл на CLK, като се използва петфазният конвейерен метод.

30). Внедряване на Bus Bridge между AHB и OCP

Предложената система се използва за проектиране на автобусен мост между два протокола, а именно общ и стандартен. Комуникационните протоколи като AHB (Advanced High-performance Bus) и OCP (Open Core Protocol) са много популярни, които се използват в приложенията на SoC (System On-chip) .

Идеи за проекти на VLSI за студенти по инженерство

Списъкът на VLSI проекти, базирани на FPGA, MatLab, IEEE и Mini Projects за студенти по инженерство, е изброен по-долу.

VLSI проекти за студенти от M. Tech

Списъкът с проекти за VLSI, базирани на M. Tech Student, включва следното.

- Областно ефективен и силно надежден RHBD базиран I0T дизайн на клетки с памет, използван в космическите приложения

- Фазов детектор с многостепенна половин скорост, използван за вериги за CLK и възстановяване на данни

- Компаратор с ниска мощност и висока скорост, използван за прецизни приложения

- Преобразувател с ниско напрежение с високоефективен и интегриран мултиплексор

- CNTFET базиран тернарен аддер с висока производителност

- Magnitude Comparator Design с ниска мощност

- Проектиране на прагова логическа порта с текущ режим за анализ на закъснението

- Декодери със смесена логика и дизайн с ниска мощност и висока производителност

- Дизайн на тестване на логиката на конвенцията за сън

- Превключвател на нивото на напрежение за приложения с двойно захранване с високоскоростен и енергийно ефективен

- Дизайн и анализ на двустранен компаратор с ниска мощност и ниско напрежение

- Флип-флоп дизайн, базиран на импулсно задействане с ниска мощност, използващ метод за подаване на сигнал

- Ефективен дизайн на вериги, базиран на преконфигурируеми FETs по време на изпълнение

- Magnitude Comparator Design с ниска мощност

- Анализ на забавяне на проектите на логически порта с праг на текущия режим

The Проекти, базирани на FPGA VLSI за студенти по инженерство и CMOS VLSI проектира мини проекти са изброени по-долу.

- Проектиране и характеризиране на втвърдени схеми на SEU за FPGA въз основа на SRAM

- Компактен CMOS базиран CMOS хибриден LUT дизайн и потенциално приложение, използван в FPGA

- Внедряване на ултразвуков сензор на FPGA за измерване на разстояние

- Внедряване на FPGA за Booth Multiplier с Spartan6 FPGA

- Дискретна вълнова трансформация, базирана на повдигане със Spartan3 FPGA

- ARM контролер в роботиката, използващ FPGA

- Базиран на FPGA UART с многоканален

- Потискане на шума на ЕКГ сигнала с помощта на FPGA

- UTMI базирана FPGA реализация и USB 2.0 протоколен слой

- Внедряване на среден филтър с Spartan3 FPGA

- Внедряване на FPGA на базата на алгоритъм на AES

- Система за предупреждение за сигурност, базирана на PIC за внедряване на FPGA със Spartan 3an

- Прилагане на FPGA за проектиране на контролера за системи за дистанционно наблюдение

- Комплект за обработка на изображения на FPGA, използващ филтриране на изображения на линейни и морфологични

- Прилагане на Spartan3 FPGA Medical Fusion Image Image

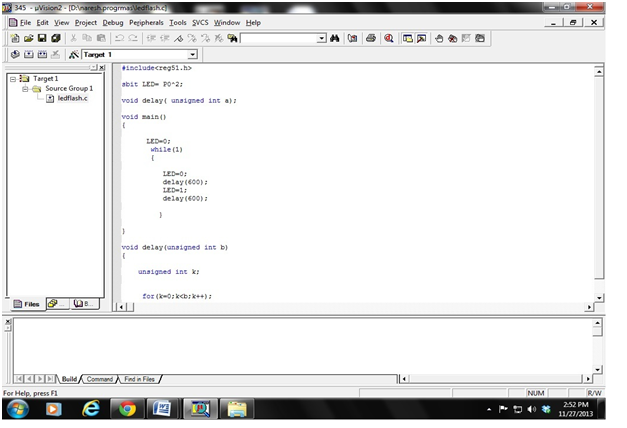

Списъкът на VLSI мини проекти, използващи VHDL код включва следното.

- Компаратор с висока скорост с използване на VLSI

- Множител на плаваща запетая, използващ VLSI

- Преобразуване на двоично в сиво VLSI

- Цифров филтър

- CLK Gating, базиран на VLSI

- Ведически множител

- CMOS FF с помощта на VLSI

- Архитектурата на паралелния процесор, използващ VLSI

- VLSI базиран пълен добавител

- Дизайн на DRAM / динамична памет с произволен достъп, базиран на VLSI

- Оформление на SRAM въз основа на VLSI

- VLSI базиран процесор за цифров сигнал

- Мултиплексор, базиран на VLSI

- Проектиране на MAC модул, базиран на VLSI

- Диференциращ, базиран на VLSI

- Базирано на VLSI БПФ или бързо преобразуване на Фурие

- Архитектурата на дискретна косинусна трансформация, базирана на VLSI

- 16-битов дизайн на множител, използващ VLSI19

- VLSI проектиране на FIFO буфер

- Високоскоростен ускорител, базиран на VLSI

VLSI проекти, използващи MATLAB и Xilinx

Списъкът на VLSI проекти, базирани на MATLAB и VLSI проекти, използващи Xilinx, включва следното.

- Проектиране и анализ на CDMA модем с MATLAB

- Проектиране на FIR филтър с използване на VHDL на FPGA и MATLAB анализ

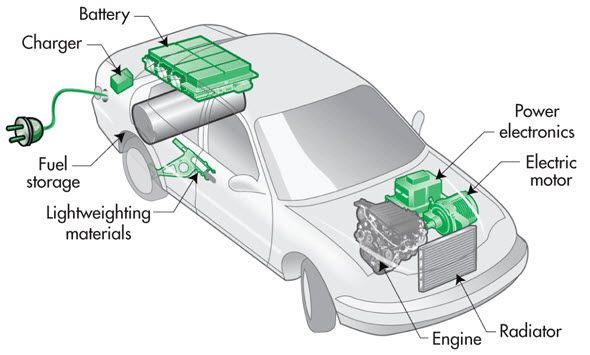

- ModelSim & Matlab или Simulink базирана симулация на система за автомобилно инженерство

- Базирани на Xilinx добавки като Ripple Carry & Carry Skip

- Аритметична единица, базирана на 32-битова плаваща точка

- ALU на базата на плаваща запетая

- RISC процесор, базиран на 32-битов

- Конволюционни възможности на ортогоналния код

- Автомати, базирани на Xilinx и Verilog

- Базирани на Xilinx паралелни префиксни добавители с 256 бита

- Протокол за взаимно удостоверяване чрез Xilinx

- Структура за достъп с единичен цикъл за логически тест, използвайки Xilinx

- UTMI и протокол, базиран на USB2.0 с помощта на Xilinx

- Конфигуриране на компресия и декомпресия на данни с помощта на Xilinx FPGA

- Базирани на Xilinx 4000 BIST и FPGA от серия Spartan

- IIR филтър, базиран на MATLAB & VLSI

- FIR филтър с помощта на MATLAB

Проекти на IEEE

The списък на IEEE VLSI проекти е посочен по-долу.

- VLSI базирана безжична система за домашна автоматизация, използваща Bluetooth

- Премахване на импулсен шум в изображението чрез използване на ефективна архитектура на VLSI

- Архитектурата на процесор в паметта за мултимедийна компресия

- Мониторинг на температурна система с помощта на Cloud & IoT

- Внедряване на OFDM система с IFFT и FFT

- Проектиране и внедряване на кода на Хаминг с Verilog

- Разпознаване на пръстови отпечатъци въз основа на VHDL с помощта на филтър Gabor

- Аритметични функции Пренасочване с ROM в зависимост от подходите за сближаване

- Анализ на ефективността и ефективността с ниска плътност на декодера за проверка на четността в приложения с ниска мощност

- FFT архитектури с обратна връзка на Pipelined Radix-2k

- Джапанки Дизайн за VLSI приложения, използващи CMOS технология с висока производителност

- Дизайн на FIR филтър с таблица за търсене по разпределена аритметика

- VLSI базиран евтин и подобрен процесор за мащабиране на изображения

- ASIC Внедряване и дизайн на Advance Turbo Encoder & Decoder с 3GPP LTE

- Push-Pull импулсни резета с условна ниска мощност и висока скорост

- Подобрено сканиране при тестване на сканиране с ниска мощност

- Аритметичен кодер VLSI архитектура за SPIHT

- Внедряване на VHDL за UART

- Регулатор на напрежение, базиран на VLSI с ниско отпадане

- Flash ADC дизайн с подобрена схема за сравнение

- Дизайн на мултипликатора с ниска мощност със сложен логически стил на постоянно закъснение

- Double Tail Comparator с висока производителност и ниска мощност

- Система за съхранение на флаш с висока производителност в зависимост от буфер за запис и виртуална памет

- FF с ниска мощност, базиран на подхода Sleepy Stack

- LFSR оптимизация на мощността за BIST с ниска мощност, внедрена в HDL

- Проектиране и внедряване на автомати за продажба с Verilog HDL

- Дизайн на акумулатора, базиран на генерирането на модел с 3 тежести с LP-LSFR

- Декодер Reed-Solomon с висока скорост и ниска сложност

- По-бърза техника на проектиране на множител Dadda

- Цифров демодулационен приемник на FM радио

- Генериране на тестов шаблон с BIST схеми

- Внедряване на VLSI архитектура с високоскоростен тръбопровод

- Проектиране на протокол за OCP протокол на чип, използващ функционалности на шината

- Детектор на фазовата честота и дизайн на помпата за зареждане, използван за високочестотна фазова верига

- Кеш памет и дизайн на кеш контролер с VHDL

- Внедряване на компресори с ниска мощност 3-2 и 4-2, базирани на ASTRAN

- Предплатена система за фактуриране на електроенергия, използваща дизайн на чипа

- Прилагане на припокриване с използване на логическа клетка и нейния анализ на мощността

- Носете поглед напред с различен анализ на производителността на бита, използващ VHDL

- Дизайн на слоя за връзка с данни с Wi-Fi MAC Протоколи

- Внедряване на FPGA за протокол за взаимно удостоверяване с модулна аритметика

- Генериране на PWM сигнал, използвайки FPGA и променлив работен цикъл

Проекти в реално време

Списъкът на VLSI проекти в реално време включват основно VLSI мини проекти, използващи VHDL код и VLSI софтуерни проекти за студенти от ECE инженерство.

- Прагматична интеграция на кеша на редове SRAM в хетерогенна 3-D DRAM архитектура с използване на TSV

- Вградена техника за самопроверка за диагностика на неизправности при забавяне в базирани на клъстер полеви програмируеми решетки на порта

- ASIC Дизайн на сложен множител

- Евтино изпълнение на VLSI за ефективно премахване на импулсния шум

- Базиран на FPGA ШИМ за космически вектор Контролна интегрална схема за трифазно задвижване с асинхронен двигател

- VLSI Внедряване на автоматичен корелатор и CORDIC алгоритъм за OFDM базирана WLAN

- Автоматично извличане на пътя с помощта на сателитни изображения с висока разделителна способност

- VHDL дизайн за сегментиране на изображения с помощта на филтър Gabor за откриване на заболявания

- Турбодекодерна архитектура с ниска сложност за енергийно ефективни безжични сензорни мрежи

- Подобряване на възможностите за конволюция на ортогонален код, използвайки внедряване на FPGA

- Проектиране и изпълнение на ALU с плаваща запетая

- CORDIC Дизайн за фиксиран ъгъл на въртене

- Продукт Reed-Solomon кодове за внедряване на NAND Flash Controller на FPGA чип

- Статистическо подобрение на достъпа за четене на SRAM при използване на схеми с отрицателен капацитет

- Управление на захранването на мрежовите интерфейси MIMO на мобилни системи

- Проектиране на стандарт за криптиране на данни за криптиране на данни

- Малка мощност и ефективна площ за носене Избор на добавяне

- Синтез и внедряване на UART с помощта на VHDL кодове

- Подобрени архитектури за единица за добавяне-изваждане с плаваща запетая

- FPGA базиран 1-битов изцяло цифров предавател, използващ Delta-Sigma модулация с RF изход за SDR

- Оптимизиране на използването на верижно търсене в декодера BCH за предаване с висока честота на грешки

- Цифров дизайн на DS-CDMA предавател, използващ Verilog HDL и FPGA

- Проектиране и внедряване на ефективна архитектура на систоличния масив

- Алгоритъм за обучение по динамика на роботи, базиран на VLSI

- Универсален мултимедиен функционален дизайн на модула, използващ техниката на фалшиво потискане на захранването

- Проектиране на автобусен мост между AHB и OCP

- Поведенчески синтез на асинхронни вериги

- Оптимизация на скоростта на модифициран декодер на Viterbi, базиран на FPGA

- Внедряване на I2C интерфейс

- Умножител с висока скорост / ниска мощност, използващ усъвършенствана техника на фалшиво потискане на захранването

- Затягащо виртуално напрежение на захранващите вериги за активно намаляване на течовете и надеждност на оксида на затвора

- FPGA базиран на мощност ефективен канализатор за софтуерно дефинирано радио

- VLSI архитектура и прототип на FPGA на цифров фотоапарат за защита и удостоверяване на изображението

- Подобряване на операцията на вътрешен робот

- Проектиране и внедряване на мрежа за пермутация ON-Chip за многопроцесорна система-On-Chip

- Метод за синхронизиране на синхронизиране със скорост на символи за безжични OFDM системи с ниска мощност

- DMA контролер (директен достъп до паметта) с помощта на VHDL / VLSI

- Преконфигурируем FFT с помощта на CORDIC базирана архитектура за MIMI-OFDM приемници

- Техника за потискане на захранването за мултимедийни / DSP приложения

- Ефективността на BCH кодовете при цифрови изображения с воден знак

- Контролер с двойна скорост на предаване на данни SD-RAM

- Внедряване на Gabor филтър за разпознаване на пръстови отпечатъци с помощта на Verilog HDL

- Проектиране на практичен нанометров мащаб, излишен чрез Aware стандартна клетъчна библиотека за подобрено излишно чрез 1 вмъкване

- Алгоритъм за компресиране и декомпресиране на данни без загуби и неговата хардуерна архитектура

- Рамка за коригиране на многобитови меки грешки

- Ефективно компресиране на данни от Viterbi

- Внедряване на FFT / IFFT блокове за OFDM

- Компресиране на изображение на базата на Wavelet чрез VLSI прогресивно кодиране

- VLSI Внедряване на напълно аплициран множител По-малко 2d DCT / IDCT архитектура за Jpeg

- FPGA-базирана емулация на грешки на синхронни последователни вериги

По този начин това е всичко за списъка с VLSI проекти за инженерство, студенти по M.Tech, които са полезни при избора на темата за последния им проект. След като прекарате ценното си време, докато преглеждате този списък, ние вярваме, че имате доста добра идея да изберете избраната от вас тема от списъка на проектите на VLSI и се надяваме, че имате достатъчно увереност, за да вземете всяка тема от списък. За допълнителни подробности и помощ при тези проекти можете да ни пишете в раздела за коментари, даден по-долу. Ето въпрос към вас, какво е VHDL?

Кредит за снимки

- VLSI проекти от set-tech