В тази статия ще обсъдим много различни идеи за вериги, изградени с помощта на NAND порти от интегрални схеми като IC 7400, IC 7413, IC 4011 и IC 4093 и др.

IC 7400, IC 7413 Спецификации

I.C.s 7400 и 7413 са 14-пинови DIL интегрални схеми, или „14-пинови интегрални схеми с двойна линия“, където щифт 14 е положителното захранване V +, а щифт 7 е отрицателният, заземеният или 0 V пин.

Входовете за захранване към щифтове 14 и 7 не са показани на чертежите за по-голяма простота, но ви съветваме да не забравяте да свържете тези щифтове, иначе веригата просто няма да работи!

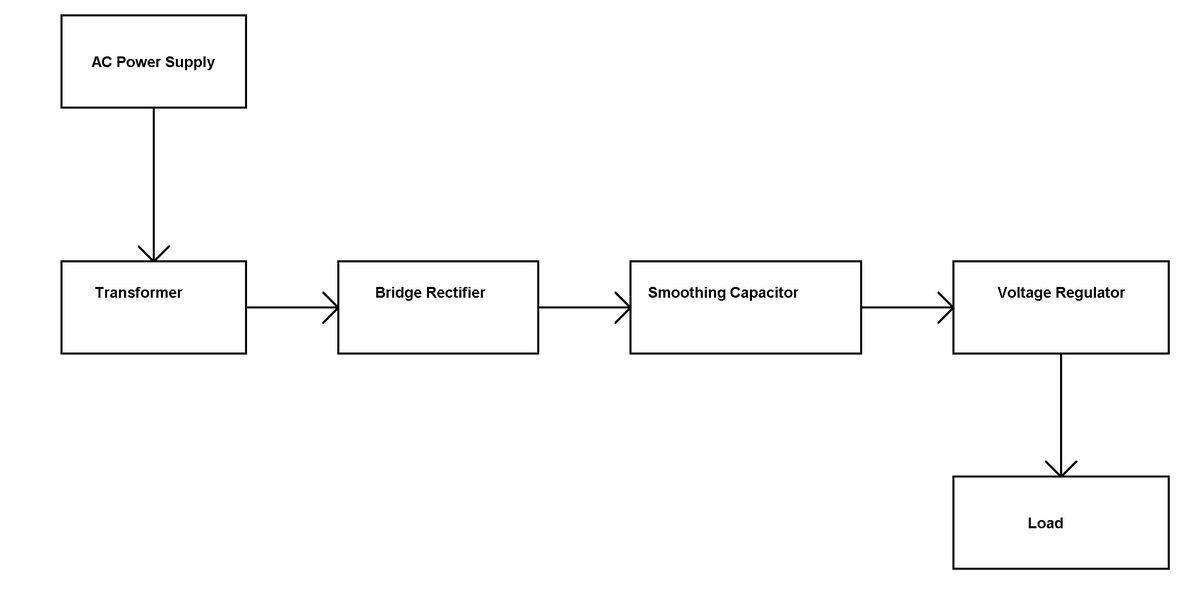

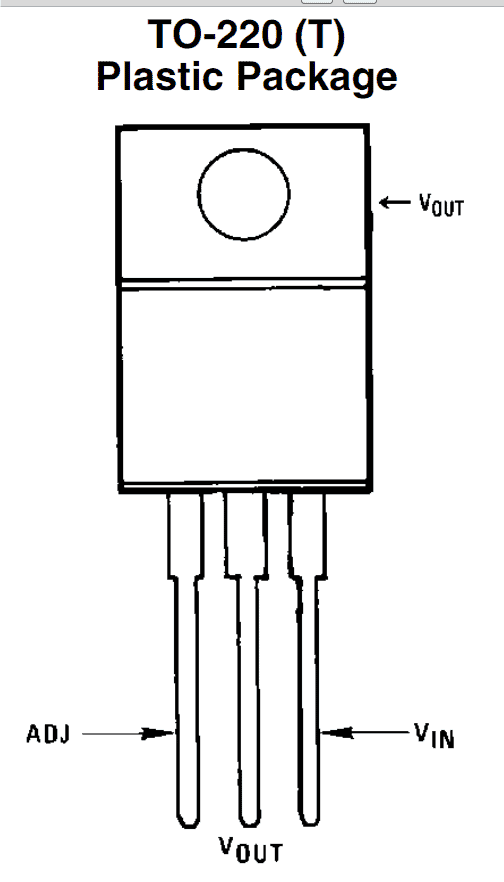

Всички вериги работят с 4,5 V или 6 V DC захранване, но типичното напрежение може да бъде 5 волта. Регулирано захранване с 5 V захранване може да бъде получено чрез редица опции.

4-те порти на 7400 са абсолютно еднакви със своите характеристики:

- Изход A изводи 1, 2 входа, извод 3 изход

- Щипки B на вход 4, 5 входа, изход 6 на изход

- Изход C изводи 10, 9 входа, извод 8 изход

- Гнездо D щифтове 13, 12 входа, извод 11 изход

Може да намерите конкретна схема, показваща осцилатор, прилагащ врати A и B, но това също означава, че същият може да бъде проектиран с използване на порта A и C, B и C или C и D, без никакви проблеми.

Фигура 1 показва логическата схема на вашия 7400 I.C. Фигура 2 демонстрира логическото символно представяне само за една порта, всяка отделна порта обикновено е „2 Input NAND Gate“.

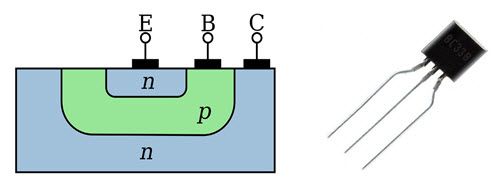

Вътрешната конфигурация с индивидуална порта е показана на фигура 3. 7400 е TTL логика I.C., което означава, че работи, като използва „Transistor-Transistor-Logic“. Всяка една порта използва четири транзистора, всеки 7400 се състои от 4 х 4 = 16 транзистора.

Логическите порти включват двойка състояния, в зависимост от двоичната система, 1 или „Висока“ обикновено 4 волта и 0 (нула) или „Ниска“ обикновено 0 волта. В случай, че не се използва терминал за порта. което може да съответства на вход 1.

Това означава, че щифтът с отворена порта е на „високо“ ниво. Когато входният щифт на порта е свързан със заземяване или 0 волта, тогава входът става 0 или логически нисък.

Вратата NAND всъщност е комбинация от 'NOT и AND' порта, когато и двата й входа (и функцията) са на логика 1, изходът е изход NOT gate, който е 1.

Изходът от NOT порта ще бъде 0V в отговор на 1 входен сигнал или + вход за захранване, което означава, че изходът ще бъде логически нулев, когато входът е на + ниво на захранване.

За NAND порта, когато и двата входа са логически 0, изходът се превръща в логика 1, което е точно като отговор на NOT порта. Може да изглежда трудно да се разбере точно защо изходът е 1, когато входовете се държат на 0, и обратно.

Може да се обясни по този начин

За превключване на състояние трябва да възникне функция И, т.е. всеки вход трябва да се трансформира за превключване на състоянието.

Това се случва само когато двата входа превключат от 0 до 1. 7400 портата са 2 входни NAND порта, но 3 входни NAND порта 7410 IC, 4 входни NAND порта 7420 и също 8 входни NAND порта 7430 също могат да бъдат доставени лесно от пазара .

Що се отнася до 7430, неговата 8 входна порта ще превключва състояние само когато всеки един от 8-те входа е или 1, или 0.

Когато 8-те входа на 7430 са 1,1,1,1,1,1,1,0, тогава изходът ще продължи да бъде 1. Промяната на състоянието няма да настъпи, докато всички 8 входа нямат идентична логика .

Но веднага щом последният вход се промени от 0 на 1, изходът се променя от 1 на 0. Техниката, която причинява „промяна на състоянието“ е решаващ аспект за разбирането на функционалността на логическите вериги.

Броят на щифтовете, които логическата интегрална схема обикновено може да има, са 14 или 16. 7400 се състои от четири NAND порта, с 2 входни щифта и 1 изходен щифт за всеки от портата, както и двойка щифтове за входовете за захранване, щифт 14 и щифт 7.

IC 7400 Семейство

Останалите членове на семейството 7400 могат да идват с по-голям брой входни щифтове, като 3 входни NAND порта, 4 входни NAND порта и 8 входни NAND порта, предлагащи повече опции за комбинация на вход за всяка порта. Като пример IC 7410 е вариант на 3 входни NAND порти или 'тройна 3 входна NAND порта'.

IC 7420 е вариант на 4 входни NAND порта и се нарича още 'Dual 4 input NAND gate', докато IC 7430 е член, който има 8 входа и е известен като 8-входен NAND порта.

Основни NAND портални връзки

Докато IC 7400 разполага само с NAND порта, възможно е да свържете NAND портата по редица начини.

Това ни позволява да ги преобразуваме в други форми на порта като:

(1) инвертор или „НЕ“ порта

(2) И порта

(3) ИЛИ порта

(4) НИ порта.

IC 7402 прилича на 7400, въпреки че се състои от 4 NOR порта. По същия начин, както NAND е комбинация от „NOT plus AND“, NOR е комбинация от „NOT plus OR“.

7400 е изключително адаптивна интегрална схема, както може да се намери от обхвата на схемите в ръководството за приложения.

За да ви помогне да разберете напълно функционалността на NAND порта, по-горе е демонстрирана таблица TRUTH за 2 входна NAND порта.

Еквивалентните таблици на истината могат да бъдат оценени за почти всяка логическа порта. Таблицата на истината за 8 входни порта като 7430 е малко по-сложна.

Как да тествате NAND порта

За да проверите 7400 IC, можете да приложите мощност към щифтове 14 и 7. Поддържайте щифтове 1 и 2, свързани към положително захранване, това ще покаже изхода като 0.

След това, без да променяте връзката на щифт 2, свържете щифт 1 на 0 волта. Това ще позволи на входовете да станат 1, 0. Това ще доведе до завъртане на изхода 1, осветявайки светодиода. Сега просто разменете връзките на пин 1 и пин 2, така че входовете да станат 0, 1, това ще превключи изхода на логика 1, като изключи светодиода.

В последната стъпка свържете и двата входни щифта 1 и 2 към земята или 0 волта, така че входовете да са на логика 0, 0. Това отново ще превърне изхода в логика висока или 1, като включите светодиода. Светещият светодиод означава логическо ниво 1.

Когато светодиодът е изключен, това предполага логическо ниво 0. Анализът може да се повтори за портите B, C и D.

Забележка: всяка от веригите, доказани тук, работи с 1 / 4W 5% резистори - всички електролитни кондензатори обикновено са с номинал 25V.

Ако дадена верига не работи, можете да разгледате връзките, възможността за дефектна интегрална схема може да бъде малко вероятно в сравнение с неправилно свързване на щифтовете. Тази връзка на NAND порта, показана по-долу, може да е най-основната и работи, като използва само 1 порта от 7400.

1) НЕ Порта от NAND порта

Когато входните щифтове a на NAND порта са късо помежду си, веригата тогава работи като инвертор, което означава, че изходната логика показва винаги обратното на входа.

Когато късите входни щифтове на портата са свързани към 0V, изходът ще се превърне в 1 и обратно. Тъй като конфигурацията „НЕ“ осигурява противоположна реакция през входните и изходните щифтове, оттук и името NOT gate. Тази фраза всъщност е технически подходяща.

2) Създаване и Gate от NAND Gate

Тъй като портата NAND също е вид врата „NOT AND“, следователно в случай, че вратата „NOT“ се въведе след NAND порта, веригата се превръща в порта „NOT NOT AND“.

Няколко негативи пораждат положително (понятие, което е популярно и в математическите концепции). Веригата вече се превърна в порта „И“, както е показано по-горе.

3) Изработване или порта от NAND Gates

Поставянето на NOT порта преди всеки вход на NAND порта генерира OR порта, както е показано по-горе. Това обикновено е 2-вход ИЛИ порта.

4) Изработване на NOR Gate от NAND Gates

В предишния дизайн създадохме OR порта от NAND порти. Всъщност NOR порта се превръща в NOT OR gate, когато добавяме допълнителна NOT gate непосредствено след OR gate, както е показано по-горе.

5) Тестер за ниво на логиката

Тази верига, тествана на логическо ниво, може да бъде създадена чрез единична 7400 NAND порта като инвертор или НЕ порта за индикация на логически нива. Няколко червени светодиода са използвани за разграничаване на логическите нива на светодиодите 1 и светодиодите 2.

Светодиодният щифт, който е по-дълъг, става катод или отрицателният щифт на светодиода. Когато входът е на логическо ниво 1 или HIGH, светодиодът 1 светва естествено.

Пинът 3, който е изходният щифт, е противоположен на входа при логика 0, което кара светодиода 2 да остане изключен. Когато входът получи логика 0, LED 1 се изключва по естествен път, но LED 2 сега свети поради противоположната реакция на портата.

6) БИСТИБЪЛ ЛАК (S.R. FLIP-FLOP)

Тази схема използва няколко NAND порта, кръстосано свързани, за да направи S-R бистабилна верига на резето.

Изходите са маркирани като Q и 0. Редът над Q означава НЕ. 2-те изхода Q и 0 действат като взаимно допълване. Значение, когато Q достигне логическо ниво 1, Q се превръща в 0, когато Q е 0, Q се превръща в 1.

Веригата може да се активира и в двете стабилни състояния чрез подходящ входен импулс. По същество това позволява на веригата функция „памет“ и я създава в супер лесен 1 битов (една двоична цифра) чип за съхранение на данни.

Двата входа са с марка S и R или Set and Reset, поради което тази схема обикновено е известна като S.R.F.F. ( Задайте Reset Flip-Flop ). Тази схема може да бъде доста полезна и се прилага в редица вериги.

ГЕНЕРАТОРЪТ S-R FLIP-FLOP ПРЯМЪГЪЛНИ ВЪЛНИ

Схемата SR Flip-Flop може да бъде конфигурирана да работи като генератор на квадратни вълни. Ако F.F. се прилага със синусоидална вълна, да кажем от 12V AC от трансформатор, с минимум 2 волта от пик до пик, изходът ще реагира чрез генериране на квадратни вълни с пик до пик, еквивалентен на Vcc напрежение.

Може да се очаква, че тези квадратни вълни са с идеална квадратна форма поради изключително бързите времена на нарастване и спадане на IC. Изходът на инвертора или NOT порта, подаващ към R входа, води до създаване на допълнителни ON / OFF входове през R и S входовете на веригата.

8) ПРЕВКЛЮЧВАЙТЕ КОНТАКТЕН ЕЛИМИНАТОР НА БОНС

В тази схема S-R FLIP-FLOP може да се разглежда като приложен като елиминатор на отскачане на контакта на превключвателя.

Винаги, когато контактите на превключвателя са затворени, той обикновено е последван от няколко подскачащи контакта между тях поради механично напрежение и натиск.

Това води най-вече до генериране на фалшиви шипове, които могат да причинят смущения и нестабилна работа на веригата.

Горната схема елиминира тази възможност. Когато контактите се затворят първоначално, той фиксира веригата и поради това намесата от отскока на контакта не успява да създаде никакъв ефект върху тригера.

9) РЪЧЕН ЧАСОВНИК

Това е друг вариант на схема осем. За експериментиране с вериги като половин суматор или други логически схеми, наистина е необходимо да можете да анализирате веригата, тъй като тя работи с един импулс наведнъж. Това може да се постигне чрез прилагане на ръчен часовник.

Когато превключвателят се превключва, на изхода се появява самотен спусък. Веригата работи изключително добре с двоичен брояч. Винаги, когато превключвателят е превключен, е разрешено да се случва само един импулс в даден момент поради функцията за отскачане на веригата, която позволява на броенето да напредва по един спусък наведнъж.

10) S-R FLIP-FLOP С ПАМЕТ

Тази схема е проектирана с помощта на основния S-R тригер. Изходът се определя от последния вход. D показва входа DATA.

„Активиращ“ импулс става необходим за активиране на портите B и C. Q формира идентично логическо ниво като D, което означава, че това приема стойността на D и продължава да бъде в това състояние (вижте снимка 14).

Номерата на пиновете не са дадени за простота. Всичките 5 порта са 2 входни NAND, необходими са няколко 7400. Диаграмата по-горе обозначава само логическа схема, но все пак може бързо да се преобразува в схема.

Това опростява диаграми, които включват огромни количества логически порти да работят с. Сигналът за активиране може да бъде импулс от 'ръчната тактова схема', обяснена по-рано.

Веригата работи винаги, когато се прилага сигнал „CLOCK“, това обикновено е основен принцип, използван във всички компютърни приложения. Обяснените по-горе двойки схеми могат да бъдат изградени, като се използват само две 7400 интегрални схеми, свързани помежду си.

11) ЧАСОВЕ, КОНТРОЛИРАНО FLIP-FLOP

Това всъщност е друг тип SR тригер с памет. Въвеждането на данни се управлява с тактов сигнал, а изходът през S-R Flip-Flop също се регулира от часовника.

Този Flip-Flop работи добре като регистър за съхранение. Часовникът всъщност е главен контролер за входно и изходно движение на импулсите.

12) ИНДИКАТОР И ДЕТЕКТОР С ВИСОКА СКОРОСТ

Тази конкретна схема е проектирана с помощта на S-R Flip -Flop и е свикнала да усеща и показва специфичен импулс в рамките на логическа схема.

Този импулс фиксира веригата, след което изходът се прилага към входа на инвертора, което кара червения светодиод да свети.

Веригата продължава да бъде в това конкретно състояние, докато не се елиминира чрез превключване на еднополюсен ключ, ключ за нулиране .

13) „SNAP!“ ПОКАЗАТЕЛ

Тази схема показва как да използвате S-R Flip -Flop по друг начин. Ето, две джапанки са вградени през 7 NAND порта.

Основната теория в тази схема е прилагането на S-R джапанки и линиите INHIBIT. SI и S2 образуват превключвателите, които управляват джапанките.

В момента, в който джапанката се заключи, съответният светодиод се включва и допълнителният джапанка се възпрепятства. Когато превключвателите са под формата на бутони, освобождаването на бутона води до нулиране на веригата. Използваните диоди са 0A91 или всеки друг ще направи такъв като 1N4148.

- Портове A, B, C оформят сцената за S1 и LED 1.

- Портите D, E, F представляват етап за S2 и LED 2.

- Порта G потвърждава, че линиите INHIBIT и INHIBIT работят като допълващи се двойки.

14) АУДИООСИЛАТОР С НИСКА ЧЕСТОТА

Схемата използва два NAND порта, свързани като инвертори и кръстосано свързани, за да образуват нестабилен мултивибратор.

Честотата може да бъде променена чрез увеличаване на стойността на CI и C2 (по-ниска честота) или намаляване на стойността на C1 и C2 (по-висока честота). Като електролитни кондензатори уверете се, че връзката на полярността е правилна.

Вериги петнадесет, шестнадесет и седемнадесет също са видове нискочестотни осцилатори, създадени от верига четиринадесет. Въпреки това, в тези вериги изходът е конфигуриран да накара светодиодите да мигат.

Можем да забележим, че всички тези вериги си приличат доста много. Въпреки това, в тази схема, ако се използва светодиод на изхода, ще предизвика мигане на светодиода с много бърза скорост, която може да бъде практически неразличима от нашите очи поради постоянството на зрението. Този принцип се използва в джобни калкулатори .

15) ДВОЙНА LED МИГАЧКА

Тук включваме няколко NAND порта за създаване на много нискочестотен осцилатор. The дизайнът контролира два червени светодиода карайки светодиодите да мигат с алтернативно превключване ON OFF.

Веригата работи с два NAND порта, останалите два порта на IC могат да бъдат използвани допълнително в рамките на една и съща верига. За тази втора верига могат да се използват различни стойности на кондензатора, за да се генерира алтернативен светодиоден мигащ етап. Кондензаторите с по-висока стойност ще накарат светодиодите да мигат по-бавно и обратно.

16) ПРОСТО LED СТРОБОСКОП

Този специфичен дизайн е произведен от петнадесета верига, която работи като стробоскоп с ниска мощност. Всъщност веригата е с висока скорост LED мигач . Червеният светодиод потрепва бързо, но окото се мъчи да различи специфичните светкавици (поради постоянството на зрението).

Не може да се очаква изходната светлина да е прекалено мощна, което означава, че стробоскопът може да работи по-добре само когато е тъмно, а не през деня.

Регулиращите променливи резистори се използват за промяна на честотата на строб, така че стробоскоп може лесно да се регулира за всяка желана скорост на строб.

Стробоскопът работи изключително добре при по-високи честоти, като променя стойността на синхронизиращия кондензатор. Светодиодът всъщност като диод е в състояние да поддържа много високи честоти с лекота. Препоръчваме да може да се приложи за заснемане на изключително високоскоростни снимки през тази схема.

17) НИСКА ХИСТЕРЕЗА SCHMITT TRIGGER

Функцията за две NAND порти може да бъде конфигурирана като a Спусък на Шмит за да създадете този специфичен дизайн. За да експериментирате с тази схема, може да искате да промените R1, за който е позициониран хистерезисен ефект .

18) ОСНОВНА ЧЕСТОТА КРИСТАЛЕН ОСЦИЛАТОР

Тази схема е монтирана като кристално контролиран осцилатор. Чифт порти са свързани като инвертори, резисторите осигуряват правилното количество отклонение за свързаните порти. Третата порта е конфигурирана като „буфер“, който предотвратява претоварването на осцилаторния етап.

Не забравяйте, че когато кристалът се използва в тази конкретна верига, той ще трепне на основната си честота, което означава, че няма да трепне при своята хармонична или обертонова честота.

В случай, че веригата работи със значително намалена честота от очакваната, това би означавало, че честотата на кристалите работи при обертон. С други думи, той може да работи с няколко основни честоти.

19) ДВЕБИТОВ ДЕКОДЪР

Тази схема представлява обикновен двубитов декодер. Входовете са през линията A и B, изходите са през линията 0, 1, 2, 3.

Вход A може да бъде като логика 0 или 1. Вход B може да бъде като логика 0 или 1. Ако A и B и двата са приложени с логика 1, това се превръща в двоичен брой от 11, който е равен на денари 3 и изхода през ред 3 високо е'.

По същия начин, A, 0 B, 0 изходен ред 0. Най-високият брой се базира на количеството входове. Най-големият брояч, използващ 2 входа, е 22 - 1 = 3. Възможно е веригата да се разшири допълнително, например ако са използвани четири входа A, B, C и D, в този случай най-големият брой ще бъде 24 - 1 = 15 и изходите са от 0 до 15.

20) ФОТО СЕНЗИТИВНА ЗАКЛЮЧВАЩА СХЕМА

Това е просто верига, базирана на фотодетектор който използва няколко NAND порта за задействане на активиращо се в мрака действие на заключване.

Когато околната светлина е по-висока от зададения праг, изходът остава незасегнат и при нулева логика. Когато тъмнината падне под зададения праг, потенциалът на входа на порта NAND го превключва на висока логика, което от своя страна фиксира окончателно изхода във висока логика.

Премахването на диода премахва фиксиращата функция и сега портите работят в тандем със светлинните реакции. Това означава, че изходът редува високо и ниско в отговор на интензитета на светлината на фотодетектора.

21) АУДИООСИЛАТОР С ДВОЙНИ ТОНИ

Следващият дизайн показва как да се изгради a двутонов осцилатор използвайки две двойки NAND порти. Два осцилаторни етапа са конфигурирани с помощта на този NAND порта, единият има висока честота, използваща 0.22 µF, а другият с нискочестотен осцилатор 0.47 uF кондензатори.

Осцилаторите, свързани помежду си по такъв начин, че нискочестотният осцилатор модулира високочестотния осцилатор. Това води до излъчващ звук което звучи по-приятно и интересно от моно тона, произведен от 2-гейтов осцилатор.

22) КРИСТАЛЕН ЧАСОВОЦИЛАТОР

Това е друго кристална базирана осцилаторна верига за използване с L.S.I. 'Чип' на IC часовник за база 50 Hz. Изходът се регулира на 500 kHz, така че за да получи 50 Hz, този изход трябва да бъде свързан към четири 7490 I.C.s по каскаден начин. След това всеки 7490 разделя последващия изход на 10, позволявайки общо разделяне от 10 000.

Това накрая произвежда изход, равен на 50 Hz (500 000 10 ÷ 10 ÷ 10+ 10 = 50). Референтната стойност от 50 Hz обикновено се получава от мрежовата линия, но използването на тази схема позволява на часовника да бъде независим от мрежовата линия и също така да получи също толкова точна база от 50 Hz.

23) КЛЮЧЕН ОСЦИЛАТОР

Тази схема е изградена от генератор на тонове и превключващ етап. Тон генераторът работи нон-стоп, но без никакъв изход на слушалката.

Обаче, щом логика 0 се появи на входния вход A, той обръща порта A към логика 1. Логиката 1 отваря порта B и честотата на звука може да достигне до слушалката.

Въпреки че тук е използвана малка кристална слушалка, тя все още може да генерира удивително силен звук. Веригата може да се приложи като зумер с електронна аларма I.C.

24) ДЕТЕКТОР НА ГРЕШКА НА НАПРЕЖЕНИЕ

Тази схема е проектирана да работи като фазов детектор през четири NAND порта. Фазовият детектор анализира два входа и генерира напрежение на грешката, което е пропорционално на разликата между двете входни честоти.

Изходът на детектора преобразува сигнала през RC мрежа, състояща се от резистор 4k7 и кондензатор 0.47uF, за да се получи напрежение с постоянна постоянна ток. Веригата на фазовия детектор работи изключително добре в P.L.L. (фазов цикъл) приложения.

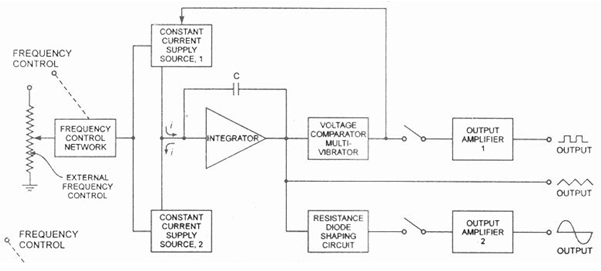

Горната диаграма показва блок-схема на пълен P.L.L. мрежа. Напрежението на грешката, генерирано от фазовия детектор, се усилва, за да регулира честотата на мултивибратора на V.C.O. (осцилатор с контролирано напрежение).

P.L.L. е невероятно полезна техника и е много ефективна при демодулация на F.M при 10,7 MHz (радио) или 6 MHz (телевизионен звук) или за възстановяване на 38 KHz подноса в стерео мултиплекс декодер.

25) RF атенюатор

Дизайнът включва 4 NAND порта и ги прилага в режим на хеликоптер за управление на диодния мост.

Диодният мост превключва или за да позволи провеждането на RF, или за блокиране на RF.

Колко RF е разрешено през канала, в крайна сметка се определя от сигнала на задвижване. Диодите могат да бъдат всякакви високоскоростни силициеви диоди или дори нашият собствен 1N4148 ще работи (вижте диаграма 32).

26) РЕФЕРЕНТЕН ЧЕСТОТЕН КЛЮЧ

Веригата работи с пет NAND порта за разработване на 2-честотен превключвател. Тук се използва бистабилна верига на резето, заедно с еднополюсен превключвател за неутрализиране на ефекта на отпадане от превключвателя SPDT. Крайният изход може да бъде f1 или f2, в зависимост от позицията на SPDT.

27) ПРОВЕРКА НА ДВЕ БИТНИ ДАННИ

Тази схема работи с концепция за компютърен тип и може да се използва за усвояване на основните логически функции, които възникват в компютъра, което води до грешки.

Проверката на грешките се извършва с добавяне на допълнителен бит (двоична цифра) в „думи“, за да може крайната сума, която се появява в компютърната „дума“, да е постоянно нечетна или четна.

Тази техника се нарича „ПРОВЕРКА НА ПАРИТЕТА“. Схемата изследва нечетен или четен паритет за 2 бита. Можем да открием, че дизайнът доста прилича на веригата за детектор на фазови грешки.

28) ДВОЙНА ПОЛОВИНОВА СЪЕДИНИТЕЛНА КРУГА

Тази схема използва седем NAND порта за създаване на половин суматор верига . A0, B0 представляват двоичните цифрови входове. S0, C0 представляват сумата и носещите линии. За да можете да научите как функционират тези видове схеми, представете си как основната математика се обучава на децата. Можете да се обърнете към таблицата на ИСТИНАТА с половин суматор по-долу.

- 0 и 0 е 0

- I и 0 е сумата 1 нося 0.

- 0 и 1 е сумата 1 нося 0.

- Аз и аз е 10 сума 0 нося 1.

1 0 не трябва да се бърка като „десет“, а се произнася като „една нула“ и символизира 1 x 2 ^ 1 + (0 x 2 ^ 0). Две цели половини разширителни вериги в допълнение към „ИЛИ“ порта създават пълна разширителна схема.

На следващата диаграма A1 и B1 са двоичните цифри, C0 е пренасянето от предишния етап, S1 става сумата, C1 е пренасянето към следващия етап.

29) НИ ПОЛОСЪЕДИНИТЕЛ НА ПОРТА

Тази верига и следващите по-долу са конфигурирани, използвайки само NOR порти. 7402 IC се предлага с четири NOR порта с 2 входа.

Половината суматор работи с помощта на пет NOR порта, както е показано по-горе.

Изходни линии:

30) НИ ПЪЛЕН АДДЕР

Този дизайн изобразява пълна сумарна схема, използваща двойка NOR-полусумари на порта, заедно с няколко допълнителни NOR-порта. Веригата работи с общо 12 NOR порти и нужди във всички 3nos от 7402 I.C.s. Изходните линии са:

Входни линии A, B и K.

K всъщност е цифрата, която се пренася от предишния ред. Забележете, че изходът е реализиран с помощта на няколко NOR порта, които са равни на единична ИЛИ порта. Веригата се урежда обратно до две полусумари в допълнение към ИЛИ порта. Можем да сравним това с нашите преди обсъдени схеми.

31) ПРОСТО СИГНАЛЕН ИНЖЕКТОР

Основен сигнален инжектор които могат да се използват за тестване на неизправности на аудио оборудването или други проблеми, свързани с честотата, могат да бъдат създадени с използване на две NAND порта. Устройството използва 4,5V волта през 3nos от 1,5V AAA клетки последователно (вижте диаграма 42).

Друга схема на инжектор на сигнала може да бъде изградена, както е показано по-долу, използвайки половин 7413 IC. Това е по-надеждно, тъй като използва спусъка на Schmitt като мултивибратор

32) ПРОСТО УСИЛВАТЕЛ

Двойка NAND порти, проектирани като инвертори, могат да бъдат свързани последователно за разработване на прост аудио усилвател . Резисторът 4k7 се използва за генериране на отрицателна обратна връзка във веригата, въпреки че това не помага за премахване на всички изкривявания.

Изходът на усилвателя може да се използва с всеки високоговорител с мощност от 25 до 80 ома. Може да се изпробва високоговорител с 8 ома, въпреки че това може да доведе до много по-топла интегрална схема.

По-ниски стойности за 4k7 също могат да се опитат, но това може да доведе до по-нисък обем на изхода.

33) ЧАСОВНИК С НИСКА СКОРОСТ

Тук се използва спусък на Schmitt заедно с нискочестотен осцилатор, RC стойностите определят честотата на веригата. Тактовата честота е около 1 Hz или 1 импулс в секунда.

34) NAND Gate Touch Switch Switch

Само няколко NAND могат да се използват за създаване на сензорно реле превключвател за управление, както е показано по-горе. Основната конфигурация е същата като RS flip flip, обяснена по-рано, която задейства изхода си в отговор на двете сензорни подложки на техните входове. Докосването на тъчпада 1 кара изхода да се активира високо, активирайки етапа на релейния драйвер, така че свързаният товар да е включен.

Когато се докосне долната тъчпад, тя нулира изхода, връщайки го обратно на логическа нула. Това действие изключва реле шофьор и натоварването.

35) PWM контрол с помощта на един NAND Gate

NAND портите могат да се използват и за постигане на ефективна ШИМ контролирана мощност от минимум до максимум.

Показаният отляво NAND порта прави две неща, генерира необходимата честота и също така позволява на потребителя да променя отделно времето за включване и времето за изключване на честотните импулси чрез два диода, които контролират времето за зареждане и разреждане на кондензатора С1.

Диодите изолират двата параметъра и позволяват управлението на зареждането и разреждането на C1 поотделно чрез настройките на гърнето.

Това от своя страна позволява да се управлява дискретно PWM дискретно чрез настройките на пота. Тази настройка може да се използва за точен контрол на скоростта на двигателя с постоянен ток с минимални компоненти.

Удвоител на напрежение, използващ NAND Gates

NAND портите също могат да бъдат приложени за постигане на ефективност вериги за удвояване на напрежение както е показано по-горе. Nand N1 е конфигуриран като генератор на часовник или генератор на честота. Честотата е подсилена и буферирана през останалите 3 паралелни порта, свързани паралелно.

След това изходът се подава към удвоител на напрежение на диоден кондензатор или умножител, за да се извърши най-накрая 2X промяна на нивото на напрежението на изхода. Тук 5V се удвоява до 10V, но друго ниво на напрежение максимум до 15V и също се използва за получаване на необходимото умножение на напрежението.

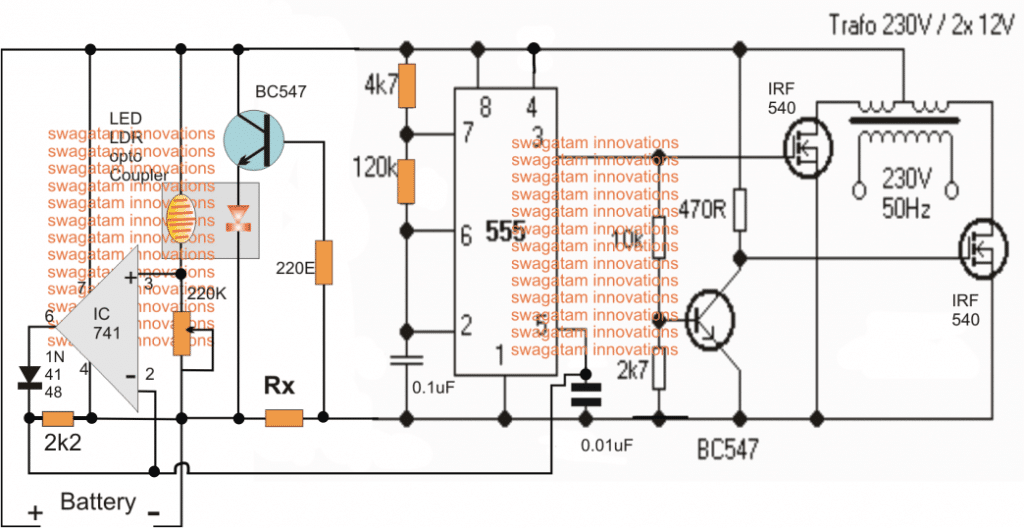

220V инвертор, използващ NAND Gates

Ако мислите, че портата NAND може да се използва само за създаване на вериги с ниско напрежение, може да грешите. Една единична IC 4011 може бързо да се приложи за създаване на мощна 12V до 220V инвертор както е показано по-горе.

N1 портата заедно с RC елементите формират основния 50 Hz осцилатор. RC частите трябва да бъдат избрани по подходящ начин, за да се получи предвидената честота 50 Hz или 60 Hz.

N2 до N4 са разположени като буфери и инвертори, така че крайният изход в основите на транзисторите да произвежда последователно превключващ ток за необходимото действие на издърпване върху трансформатора през транзисторните колектори.

Пиезо зумер

Тъй като порталите NAND могат да бъдат конфигурирани като ефективни осцилатори, свързаните приложения са огромни. Един от тях е пиезо зумер , който може да бъде изграден с помощта на единичен IC 4011.

Осцилаторите на NAND порта могат да бъдат персонализирани за реализиране на много различни идеи за вериги. Този пост все още не е завършен и ще бъде актуализиран с повече проекти, базирани на NAND порта, ако времето позволява. Ако имате нещо интересно, свързано с веригите на NAND порта, моля, уведомете ни, че отзивите ви ще бъдат много оценени.

Предишна: Червена LED LightStim схема за премахване на бръчки по лицето Напред: Лесни два транзисторни проекта за ученици