Процесът на проектиране на цифров хардуер се трансформира интензивно през последните няколко години. И така, малки цифрови вериги могат да бъдат внедрени чрез използване на PAL и PLA. Всяко устройство се използва за изпълнение на различни схеми които не се нуждаят от повече от броя i / ps, o / ps и продуктовите условия, които се предлагат в конкретния чип. Тези чипове са недостатъчни за сравнително скромни размери, като обикновено поддържат взаимен брой входове и изходи не повече от 32. За проектирането на тези вериги, които се нуждаят от повече входове и изходи, могат да бъдат използвани многобройни PLA / PAL или друг по-елегантен тип на чип може да се използва, наречен CPLD (сложно програмируемо логическо устройство). Чипът CPLD включва няколко верижни блока на един чип с вътрешни ресурси за окабеляване за свързване на блоковете на веригата. Всеки блок на веригата е сравним с PLA или PAL.

Какво е сложно програмируемо логическо устройство?

Съкращението на CPLD е „Сложни програмируеми логически устройства“, това е едно вид интегрална схема че дизайнерите на приложения проектират да внедрят цифров хардуер като мобилни телефони. Те могат да се справят със съзнателно по-високи проекти от SPLD (прости програмируеми логически устройства), но предлагат по-малко логика от FPGA ( полеви програмируеми масиви на порта ) .CPLD включват множество логически блокове, всеки от блоковете включва 8-16 макроклетки. Тъй като всеки логически блок изпълнява определена функция, всички макроклетки в логически блок са напълно свързани. В зависимост от употребата тези блокове могат или не могат да бъдат свързани помежду си.

Сложно програмируемо логическо устройство

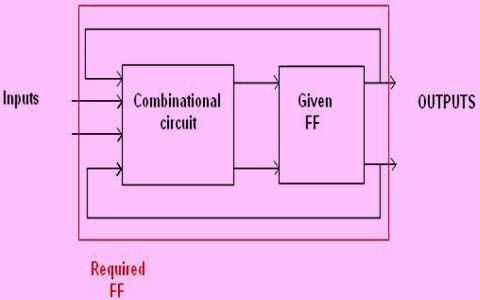

Повечето CPLD (сложни програмируеми логически устройства) имат макроклетки със сбор от логическа функция и избираем елемент FF (джапанка) . В зависимост от чипа, комбинаторната логическа функция поддържа от 4 до 16 продуктови термина с включен вентилатор. CPLD също се различават по отношение на регистрите за смяна и логическите порти. Поради тази причина вместо FPGA могат да се използват CPLD с огромен брой логически порти. Друга спецификация на CPLD означава броя на продуктовите термини, които макроклетката може да изпълни. Продуктовите термини са продукт на цифрови сигнали, които изпълняват определена логическа функция.

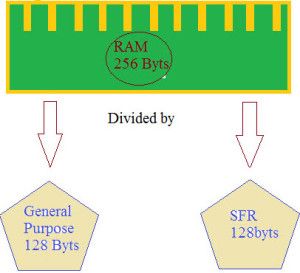

CPLD се предлагат в няколко форми на IC пакети и логически семейства. CPLD също се различават по отношение на захранващото напрежение, работния ток, резервния ток и разсейването на мощността. Освен това те се получават с различни количества памет и различни видове поддръжка на паметта. Обикновено паметта се изразява в битове / мегабита. Поддръжката на паметта се състои от ROM, RAM и RAM с два порта. Той също така се състои от CAM (съдържаща адресируема памет), както и FIFO (first-in, first-out) памет и LIFO (last-in, last-out) памет.

Архитектура на сложно програмируемо логическо устройство

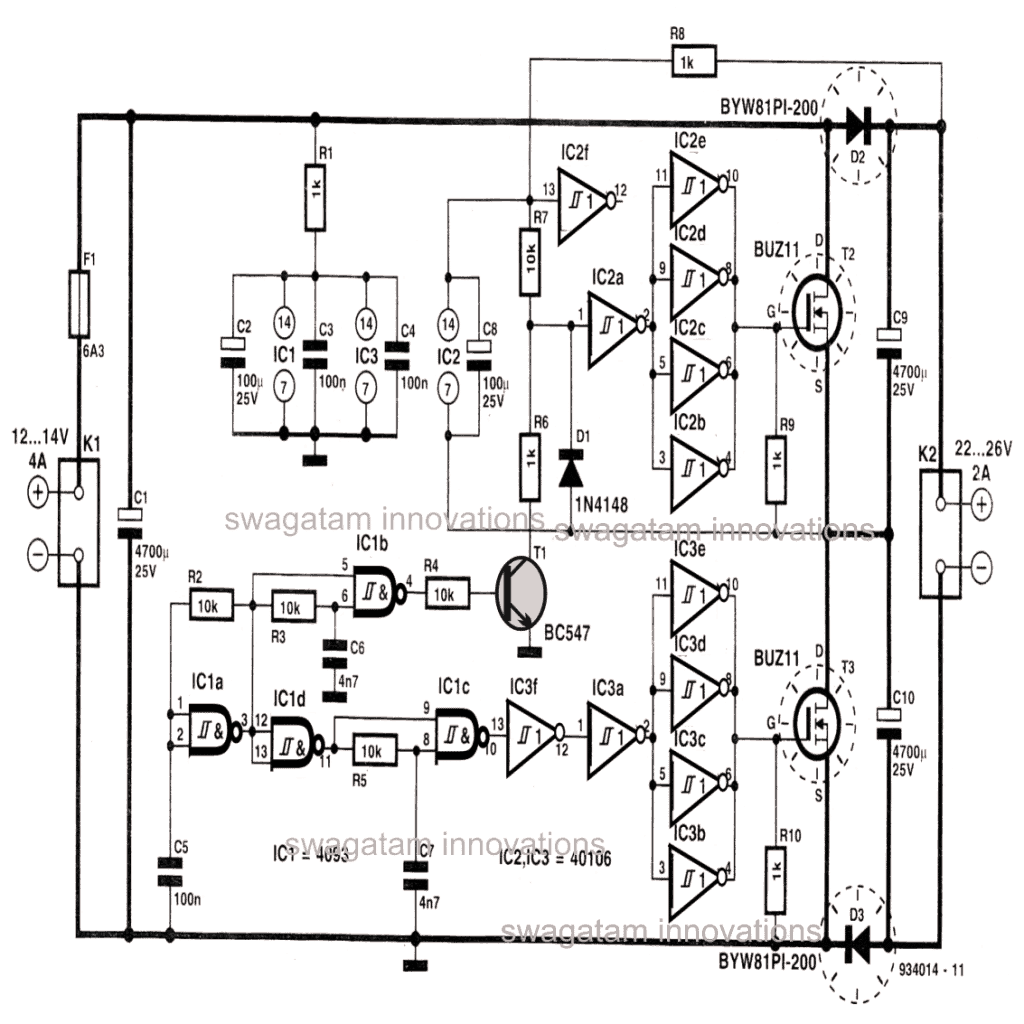

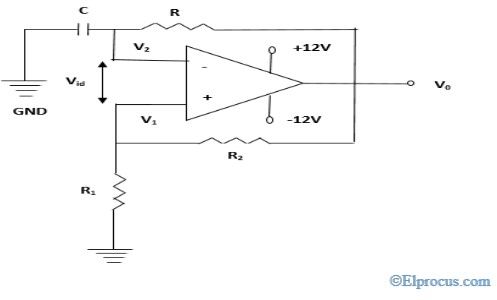

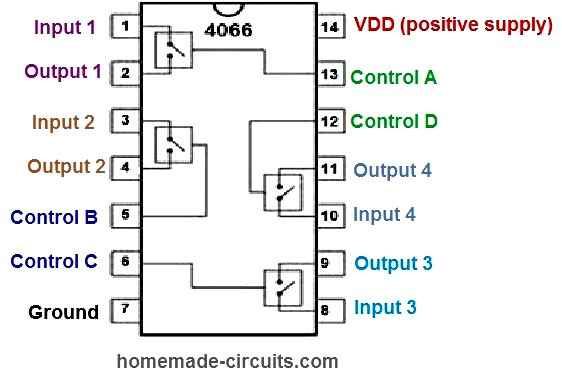

Сложно програмируемо логическо устройство се състои от група програмируеми FB (функционални блокове). Входовете и изходите на тези функционални блокове са свързани заедно чрез GIM (глобална матрица за взаимно свързване). Тази матрица за взаимно свързване може да се преконфигурира, така че да можем да модифицираме контактите между функционалните блокове. Ще има някои входни и изходни блокове, които ни позволяват да обединим CPLD с външния свят. Архитектурата на CPLD е показана по-долу.

Като цяло програмируемият FB изглежда като масив от логически порти , където масив от И порти може да бъде програмиран и ИЛИ портите са стабилни. Но всеки производител има своя начин на мислене, за да проектира функционалния блок. Изброен o / p може да бъде намерен чрез управление на сигналите за обратна връзка, получени от изходите на ИЛ порта.

Архитектура на CPLD

При програмирането на CPLD дизайнът първо се кодира на Verilog или VHDL език, след като кодът се (симулира и синтезира. По време на синтеза се подбира моделът CPLD (целево устройство) и се създава списък с мрежови карти на базата на технология. Този списък може да бъде близък -приспособяване към оригиналната архитектура на CPLD, използвайки процес на място и маршрут, обикновено постигнат от софтуера за място и маршрут на собствеността на компанията CPLD. Тогава операторът ще извърши някои процеси за потвърждение. Ако всичко е наред, той ще използва CPLD, в противен случай той ще го пренареди.

Архитектурни въпроси на CPLD

Когато се обмисля сложно програмируемо логическо устройство за използване при проектирането, има някои следните архитектурни проблеми, които могат да бъдат взети под внимание

- Технологията за програмиране

- Възможността на функционалния блок

- Възможността за I / O

Някои от семействата на CPLD от различни търговци на дребно включват

- Altera MAX 7000 и MAX 9000 семейства

- Atmel ATF и ATV семейства

- Решетка isp LSI семейство

- Решетка (Vantis) семейство MACH

- Xilinx XC9500 семейство

Семейства на CPLD

Приложения на CPLD

Приложенията на CPLD включват следното

- Сложните програмируеми логически устройства са идеални за приложения с висока производителност, критично управление.

- CPLD може да се използва в дигитален дизайн, за да изпълнява функциите на boot loader

- CPLD се използва за зареждане на данните за конфигурация на полеви програмируем масив на порта от енергонезависима памет.

- Като цяло те се използват в малки дизайнерски приложения като декодиране на адреси

- CPLD често се използват в много приложения, като например при чувствителни към разходите преносими устройства, работещи с батерии, поради малкия си размер и използването на ниска мощност.

По този начин става въпрос за сложна програмируема архитектура на логическо устройство и нейните приложения. Надяваме се, че сте разбрали по-добре тази концепция. Освен това, всякакви въпроси относно тази концепция или за изпълнение на всякакви електрически и електронни проекти , моля, дайте вашите ценни предложения, като коментирате в раздела за коментари по-долу. Ето въпрос към вас, каква е разликата между CPLD и FPGA?

Кредити за снимки:

- CPLD wikimedia

- Архитектура на CPLD slidesharecdn