MOS транзисторът е най-фундаменталният елемент в мащабния дизайн на интегрални схеми. Тези транзистори обикновено се класифицират в два типа PMOS и NMOS. Комбинацията от NMOS и PMOS транзистори е известна като a CMOS транзистор . Различното логически порти & други цифрови логически устройства, които се изпълняват трябва да имат PMOS логика. Тази технология е евтина и има добра устойчивост на смущения. Тази статия обсъжда един от видовете MOS транзистори като PMOS транзистор.

Какво е PMOS транзистор?

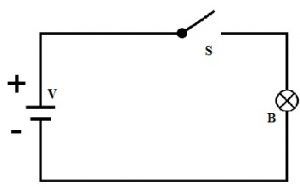

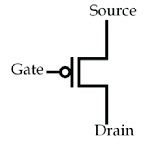

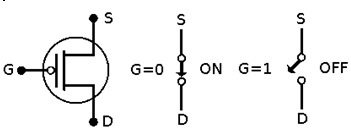

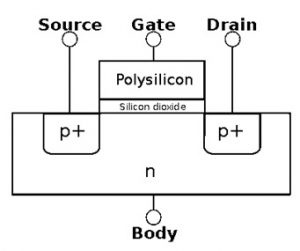

Транзисторът PMOS или металооксидният полупроводник с P-канал е вид транзистор, при който добавките от p-тип се използват в областта на канала или портата. Този транзистор е точно обратното на NMOS транзистора. Тези транзистори имат три основни терминала; източникът, портата и изтичането, където сорсът на транзистора е проектиран с p-тип субстрат, а дренажният терминал е проектиран с n-тип субстрат. В този транзистор носителите на заряд като дупки са отговорни за провеждането на ток. Символите на PMOS транзисторите са показани по-долу.

Как работи PMOS транзисторът?

Работата на p-тип транзистора е точно противоположна на n-тип транзистора. Този транзистор ще образува отворена верига, когато получи непренебрежимо малко напрежение, което означава, че няма поток от електричество от клемата на портата (G) към източника (S). По подобен начин този транзистор образува затворена верига, когато получи напрежение около 0 волта, което означава, че токът протича от терминала на портата (G) към дренажа (D).

Този балон е известен още като инверсионен балон. Така че основната функция на този кръг е да обърне стойността на входното напрежение. Ако терминалът на портата осигурява напрежение 1, тогава този инвертор ще го промени на нула и ще функционира веригата по съответния начин. Така че функцията на PMOS транзистора и NMOS транзистора е доста противоположна. След като ги обединим в една MOS верига, тогава тя ще стане CMOS (допълнителен металооксиден полупроводник) верига.

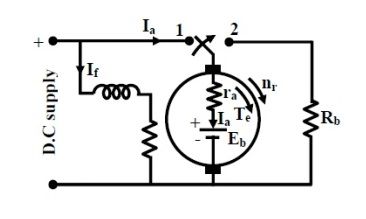

Напречно сечение на PMOS транзистор

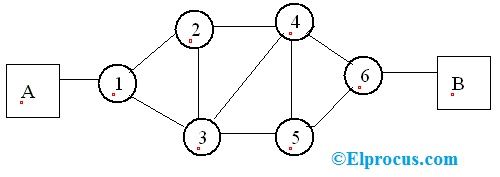

Напречното сечение на PMOS транзистора е показано по-долу. pMOS транзисторът е изграден с тяло от n-тип, включващо две полупроводникови области от p-тип, които са в съседство с портата. Този транзистор има управляващ гейт, както е показано на диаграмата, който контролира потока на електроните между двата терминала като източник и изтичане. В pMOS транзистора тялото се поддържа при +ve напрежение. След като клемата на портата е положителна, тогава клемите източник и дренаж са обратно предубедени. След като това се случи, няма поток от ток, така че транзисторът ще бъде изключен.

След като захранването на напрежението на терминала на портата се понижи, тогава положителни носители на заряд ще бъдат привлечени към дъното на Si-SiO2 интерфейса. Всеки път, когато напрежението стане достатъчно ниско, тогава каналът ще бъде обърнат и ще създаде проводяща пътека от терминала на източника към дренажа, като позволява протичането на ток.

Всеки път, когато тези транзистори се занимават с цифрова логика, обикновено има две различни стойности само като 1 и 0 (ON и OFF). Положителното напрежение на транзистора е известно като VDD, което представлява логическата висока (1) стойност в цифровите схеми. Нивата на напрежение на VDD в TTL логика обикновено бяха около 5V. Понастоящем транзисторите всъщност не могат да издържат на такива високи напрежения, тъй като те обикновено варират от 1,5 V – 3,3 V. Ниското напрежение често е известно като GND или VSS. И така, VSS означава логиката '0' и също така е настроена нормално на 0V.

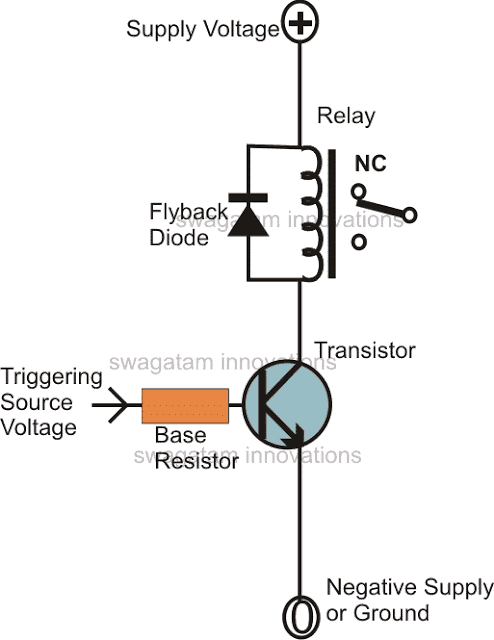

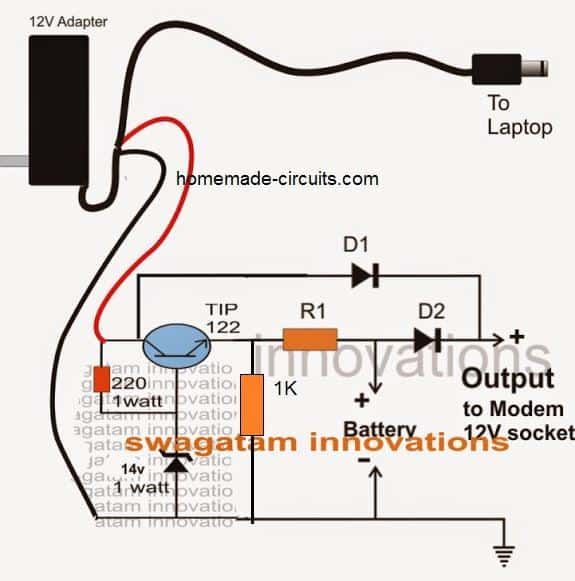

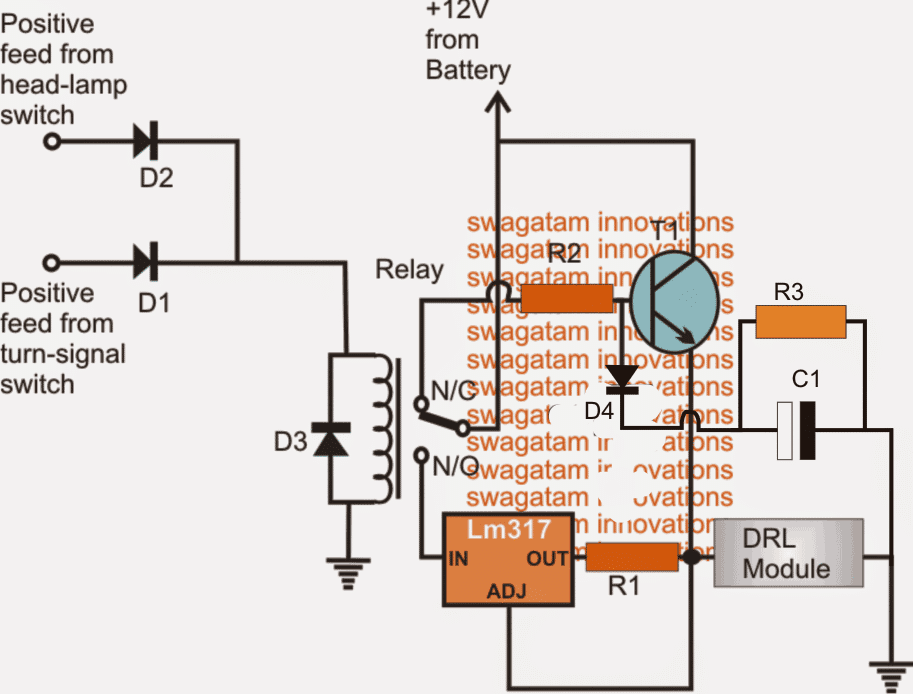

PMOS транзисторна верига

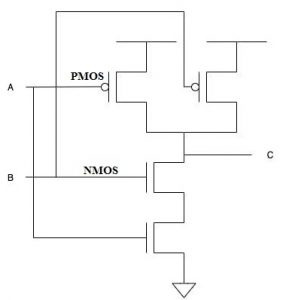

Дизайнът на NAND порта, използващ PMOS транзистор и NMOS транзистор, е показан по-долу. Като цяло NAND портата в цифровата електроника е логическа врата, която също се нарича NOT-AND gate. Изходът на този гейт е нисък (0) само ако двата входа са високи (1) и неговият изход е допълнение към И порта. Ако някой от двата входа е НИСКО (0), тогава той дава високи изходни резултати.

В логическата схема по-долу, ако входът A е 0 и B е 0, тогава входът на pMOS ще произведе „1“, а входът на nMOS ще произведе „0“. И така, тази логическа врата генерира логическа „1“, тъй като е свързана към източника чрез затворена верига и отделена от GND чрез отворена верига.

Когато A е „0“ и B“ е „1“, тогава входът на pMOS ще генерира „1“, а входът на NMOS ще генерира „0“. По този начин тази порта ще произведе логическа, защото е свързана към източника чрез затворена верига и отделена от GND чрез отворена верига. Когато A е „1“ и B е „0“, тогава входът „B“ на pMOS ще генерира висок изход (1), а входът „B“ на NMOS ще генерира изход като нисък (0). И така, тази логическа врата ще генерира логическа 1, защото е свързана към източника чрез затворена верига и отделена от GND чрез отворена верига.

Когато A е „1“ и B е „1“, тогава входът на „pMOS“ ще произведе нула, а входът на nMOS ще генерира „1“. Следователно трябва да проверим входа B на pMOS & nMOS също. B входът на pMOS ще генерира „0“, а B входът на nMOS ще генерира „1“. И така, тази логическа врата ще генерира логическа „0“, тъй като е отделена от източника чрез отворена верига и е свързана към GND чрез затворена верига.

Таблица на истината

Таблицата на истината на горната логическа схема е дадена по-долу.

|

А |

б |

° С |

|

0 |

0 | 1 |

|

0 |

1 | 1 |

| 1 | 0 |

1 |

| 1 | 1 |

0 |

Праговото напрежение на PMOS транзистора обикновено е „Vgs“, което е необходимо за създаване на канал, известен като инверсия на канала. В PMOS транзистор, субстратът и изходните клеми са просто свързани към „Vdd“. Ако започнем да намаляваме напрежението чрез позоваване на изходния извод на изходния извод от Vdd до точка, където забележите инверсия на канала, в тази позиция, ако анализирате Vgs и източника, които са с висок потенциал, тогава ще получите отрицателна стойност. И така, PMOS транзисторът има отрицателна Vth стойност.

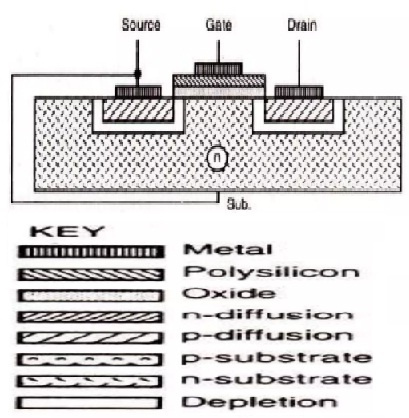

Процес на производство на PMOS

Стъпките, включени в производството на PMOS транзистор, са обсъдени по-долу.

Етап 1:

Тънък слой силициева пластина се променя в материал от N-тип чрез просто допиране на фосфорен материал.

Стъпка 2:

Плътен слой от силициев диоксид (Sio2) се отглежда върху цялостен p-тип субстрат.

Стъпка 3:

Сега повърхността е покрита с фоторезист върху дебелия слой силициев диоксид.

Стъпка 4:

След това този слой просто се излага на ултравиолетова светлина през маска, която дефинира онези области, в които трябва да се извърши дифузия заедно с транзисторните канали.

Стъпка 5:

Тези региони са гравирани взаимно с подлежащия силициев диоксид, така че повърхността на пластината да е изложена в рамките на прозореца, определен от маската.

Стъпка 6:

Останалият фоторезист се отделя и тънък слой Sio2 се отглежда обикновено с дебелина 0,1 микрометра върху цялата повърхност на чипа. След това върху него се поставя полисилиций, за да се оформи структурата на портата. Фоторезистът се поставя върху целия полисилициев слой и излага UV светлина през маската2.

Стъпка 7:

Дифузиите се постигат чрез нагряване на пластини до максимална температура и преминаване на газ с желани примеси от p-тип като бор.

Стъпка 8:

Отглежда се силициев диоксид с дебелина 1 микрометър и върху него се отлага фоторезистен материал. Изложете ултравиолетовата светлина с mask3 върху предпочитаните зони на портата, източника и дренажа, които са гравирани, за да направят контактните разрези.

Стъпка 9:

Сега върху повърхността му с дебелина 1 микрометър се отлага метал или алуминий. Отново фоторезистентният материал се отглежда върху целия метал и се излага на ултравиолетова светлина през маска4, която е гравирана, за да формира необходимия дизайн на взаимно свързване. Окончателната PMOS структура е показана по-долу.

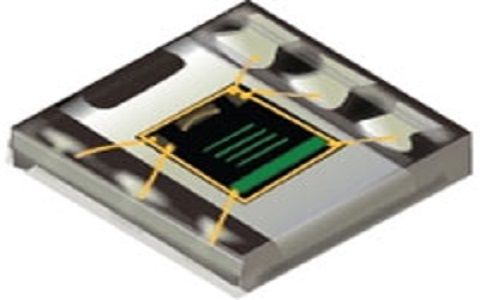

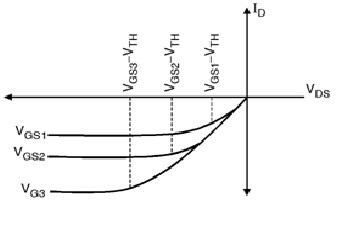

Характеристики на PMOS транзистор

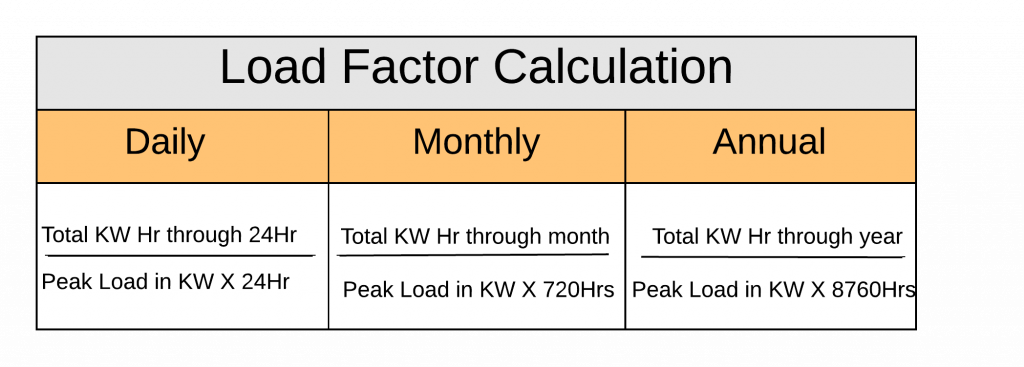

I-V характеристиките на PMOS транзистора са показани по-долу. Тези характеристики са разделени на две области, за да се получи връзката между тока на изтичане към източника (I DS), както и неговите терминални напрежения като линейни области и области на насищане.

В областта на облицовката, IDS ще се увеличи линейно, когато VDS (напрежението от оттичане към източника) се увеличи, докато в областта на насищане I DS е стабилна и е независима от VDS. Основната връзка между ISD (източник към изтичане на ток) и неговите терминални напрежения се извлича чрез подобна процедура на NMOS транзистора. В този случай единствената промяна ще бъде, че носителите на заряд, присъстващи в инверсионния слой, са просто дупки. Когато дупките се движат от източник към изтичане, тогава потокът от ток също е същият.

Така отрицателният знак се появява в текущото уравнение. В допълнение, всички приложени отклонения на клемите на устройството са отрицателни. И така, характеристиките на ID на транзистора PMOS - VDS са показани по-долу.

Уравнението на изтичащия ток за PMOS транзистор в линейната област е дадено като:

ID = – mp Кокс

По същия начин, уравнението на дрейн тока за PMOS транзистор в областта на насищане е дадено като:

ID = – mp Cox (VSG – | V TH |p )^2

Където „mp“ е подвижността на отвора и „|VTH| p’ е праговото напрежение на PMOS транзистора.

В горното уравнение отрицателният знак ще покаже, че ID( ток на изтичане ) тече от дренажа (D) към източника (S), докато дупките текат в обратната посока. Когато мобилността на дупката е ниска в сравнение с мобилността на електроните, тогава PMOS транзисторите страдат от способността на задвижването с нисък ток.

По този начин, това е всичко за общ преглед на PMOS транзистор или p-тип mos транзистор - производство, верига и неговата работа. PMOS са проектирани транзистори с p-източник, n-субстрат и изтичане. Носителите на заряда на PMOS са дупки. Този транзистор провежда, след като към терминала на портата се приложи ниско напрежение. PMOS-базираните устройства са по-малко податливи на смущения в сравнение с NMOS устройствата. Тези транзистори могат да се използват като резистори с контролирано напрежение, активни товари, токови огледала, транс-импедансни усилватели, а също и в превключватели и усилватели на напрежение. Ето един въпрос за вас, какво е NMOS транзистор?