Преди да влезете в реалностите за Кодери и декодери , нека имаме кратка мисъл относно мултиплексирането. Редовно преглеждаме приложенията, където се очаква да подават няколко входни сигнала към единичен товар, всеки наведнъж. Тази процедура за избор на един от входните сигнали, които да се подават към товара, е известна като Мултиплексиране. Инвертът на тази операция, т.е. начинът за подхранване на няколко натоварвания от един общ източник на сигнал е известен като Демултиплексиране . По същия начин в цифров домейн, за простота на предаване на информация, информацията редовно се кодира или задава вътре в кодове и след това този защитен код се предава. В колектора кодираната информация се декодира или натрупва от кода и се обработва, за да бъде показана или предадена на товара по същия начин.

Декодер от 2 до 4 линии

Това възлагане на криптиране на информацията и дешифриране на информацията е завършено от кодери и декодери. Е, какво ще кажете сега да разберем какво всъщност са кодерите и декодерите.

Какво е декодер?

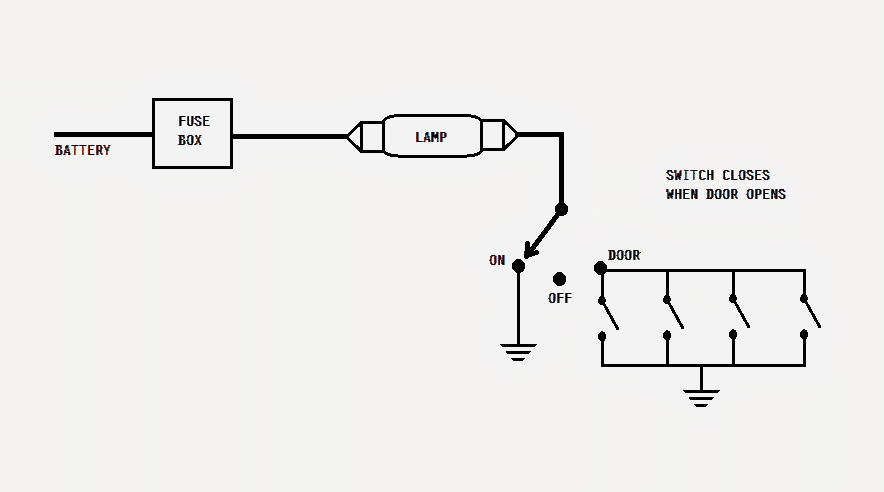

Декодерът е логическа схема с множество входове, множество изходи, която променя кодовете i / ps в кодирани o / ps, където както входовете, така и изходите са различни, например n-to-2n, и двоични кодирани десетични декодери. Декодирането е от съществено значение в приложения като мултиплексиране на данни, декодиране на адреси в паметта и 7-сегментен дисплей. Най-добрият пример за декодерна схема ще бъде AND-gate, тъй като когато всички нейни входове са „High.“, Изходът на тази порта е „High“, който се нарича „активен High output“. Като алтернатива на AND порта, NAND портата е свързана, изходът ще бъде “Low” (0) само когато всичките му входове са “High”. Такъв o / p се нарича „активна ниска мощност“.

Декодер

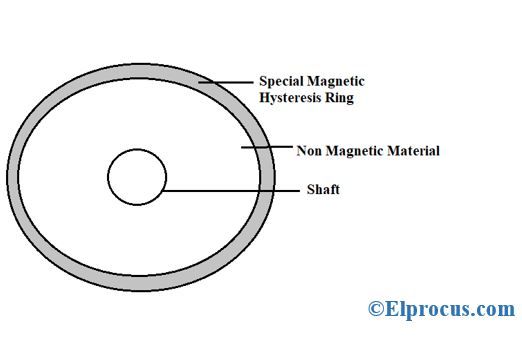

Малко по-труден декодер биха били двоичните декодери от тип n-to-2n. Този вид декодери са комбинационни схеми, които модифицират двоична информация от n-кодирани входове до повечето от 2n изключителни изходи. В случай, че тогава битово кодирани данни имат празни битови комбинации, декодерът може да има по-малко от 2n изхода. 2 до 4, Декодер от 3 до 8 линии или декодер от 4 до 16 са други примери.

Паралелното двоично число е вход към декодер, използван за забелязване появата на определено двоично число на входа. Изходът показва съществуването или несъществуването на точен номер на входа на декодера.

Проектиране на верига за декодер от 2 до 4

Подобно на схема на мултиплексор , декодерът не е ограничен до определен адресен ред и по този начин може да има повече от два изхода (с два, три или четири адресни реда). Декодерната схема може да декодира 2, 3 или 4-битово двоично число или може да декодира до 4, 8 или 16 мултиплексирани по време сигнали.

2-до-4-декодер верига

Като декодер, тази схема приема n-битово двоично число и генерира изход на една от 2n изходни линии. Следователно обикновено се описва с броя адресиране на i / p линии и броя на данни o / p линии. Типичните интегрални схеми за декодиране могат да включват две 2-4-верижни вериги, 3-8-линейна верига или a 4-16-редов декодер верига. Едно изключение за двоичния характер на тази схема са 4-10-редовите декодери, които се предлагат да променят двоично кодиран десетичен вход (BCD) към изход от 0-9.

Ако използвате тази схема като декодер, може да искате да вмъкнете ключалки за данни в o / ps, за да запазите всеки сигнал, докато останалите се предават. Но това не се отнася, когато използвате тази схема като декодер, тогава ще искате само един активен o / p, който да е равен на входния код.

Таблица на истината за декодер от 2 до 4

При този тип декодери декодерите имат два входа, а именно A0, A1 и четири изхода, обозначени с D0, D1, D2 и D3. Както можете да видите в следната таблица на истината - за всяка въведена комбинация е включен един o / p ред.

Таблица на истината от 2 до 4 дешифратора

В горния пример можете да забележите, че всеки o / p на декодера е наистина minterm, произтичащ от осигурена комбинация от входове, т.е.

D0 = A1 A0, (minterm m0), което съответства на вход 00 D1 = A1 A0, (minterm m1), което съответства на вход 01 D2 = A1 A0, (minterm m2), което съответства на вход 10 D3 = A1 A0, (minterm m3 ), което съответства на вход 11

The веригата се изпълнява с И порти , както е показано на фигурата. В тази схема логическото уравнение за D0 е A1 / A0 и т.н. По този начин, всеки изход на декодера ще бъде генериран към входната комбинация.

Приложения на декодера

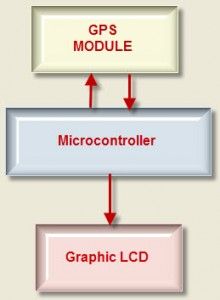

Приложенията на декодера включват в изработване на различни електронни проекти .

- Военно-полетен робот с летяща камера за нощно виждане

- Роботизиран автомобил с металдетектор

- RF-базирана система за домашна автоматизация

- Скоростна синхронизация на множество двигатели в индустриите

- Автоматична безжична система за наблюдение на здравето в болници за пациенти

- Секретен код Активирана сигурна комуникация с помощта на RF технология

Това е всичко за декодера и неговите приложения в комуникационни проекти . Вярваме, че може би сте имали по-добра представа за тази концепция. Освен това, при всякакви съмнения относно тази статия, моля, дайте своите ценни предложения, като коментирате раздела за коментари по-долу.