В тази публикация ще разберем подробно какво представляват логическите порти и как работи. Ще разгледаме основната дефиниция, символ, таблица на истината, мулти входни порти, ще изградим и еквиваленти на порта, базирани на транзистори, и накрая ще направим преглед на различни съответни интегрални схеми на CMOS.

Какво представляват Logic Gates

Логическа порта в електронна схема може да бъде изразена като физическа единица, представена чрез булева функция.

С други думи, логическата порта е проектирана да изпълнява логическа функция, използвайки единични или повече двоични входове и да генерира единичен двоичен изход.

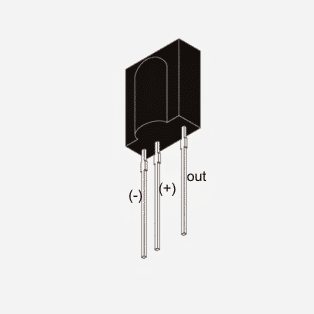

Електронните логически порти са основно конфигурирани и изпълнени с помощта на полупроводникови блокове или елементи като диоди или транзистори, които работят като превключватели ON / OFF с добре дефиниран модел на превключване. Логическите порти улесняват каскадирането на портите, така че лесно дават възможност за съставяне на булеви функции, което прави възможно създаването на физически модели на цялата булева логика. Това допълнително дава възможност за записване на алгоритми и математика, използвайки логическа логика.

Логическите вериги могат да използват полупроводникови елементи в обхвата на мултиплексори, регистри, аритметични логически модули (ALU) и компютърна памет и дори микропроцесори, включващи до 100 милиона логически порта. В днешното изпълнение ще откриете предимно полеви транзистори (полеви транзистори), които се използват за производство на логически портали, добър пример са полевите транзистори от метал-оксид-полупроводник или MOSFET.

Нека започнем урока с логика И порти.

Какво е Logic “AND” Gate?

Това е електронна порта, чийто изход се превръща в „висок“ или „1“ или „истински“ или издава „положителен сигнал“, когато всички входове на портата И са „високи“ или „1“ или „вярно“ или „ положителен сигнал ”.

Например: Кажете в AND порта с ‘n’ брой входове, ако всички входове са „високи“, изходът се превръща в „висок“. Дори ако един вход е “LOW” или “0” или “false” или “negative signal”, изходът се превръща в “LOW” или “0” или “false” или издава “отрицателен сигнал”.

Забележка:

Понятието „Високо“, „1“, „положителен сигнал“, „вярно“ по същество е същото (Положителният сигнал е положителният сигнал на батерията или захранването).

Понятието „LOW“, „0“, „отрицателен сигнал“, „false“ по същество са еднакви (отрицателен сигнал е отрицателният сигнал на батерията или захранването).

Илюстрация на символа на логиката и портата:

Тук „A“ и „B“ са двата входа и „Y“ се извежда.

Булевият израз за логика И порта: Изходът „Y“ е умножение на двата входа „A“ и „B“. (A.B) = Y.

Булевото умножение се обозначава с точка (.)

Ако „A“ е „1“, а „B“ е „1“, изходът е (A.B) = 1 x 1 = „1“ или „висок“

Ако „A“ е „0“, а „B“ е „1“, изходът е (A.B) = 0 x 1 = „0“ или „Low“

Ако „A“ е „1“, а „B“ е „0“, изходът е (A.B) = 1 x 0 = „0“ или „Low“

Ако „A“ е „0“, а „B“ е „0“, изходът е (A.B) = 0 x 0 = „0“ или „Low“

Горните условия са опростени в таблицата на истината.

Таблица на истината (два входа):

| A (вход) | B (ВХОД) | Y (изход) |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

3-входна „И“ порта:

Илюстрация на 3 вход и порта:

Логическите И порти могат да имат ‘n’ брой входове, което означава, че могат да имат повече от два входа (Логическите И порти ще имат поне два входа и винаги един изход).

За 3 вход И порта булевото уравнение се превръща по следния начин: (A.B.C) = Y, подобно за 4 вход и по-горе.

Таблица на истината за 3 входна логика И порта:

| A (ВХОД) | B (ВХОД) | C (ВХОД) | Y (ИЗХОД) |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

Многовходна логика и порти:

Наличните в търговската мрежа Logic AND порта са налични само в 2, 3 и 4 входа. Ако имаме повече от 4 входа, тогава трябва да каскадираме портите.

Можем да имаме шест входни логически И порта, като каскадираме 2-те входни И порта, както следва:

Сега булевото уравнение за горната верига става Y = (A.B). (C.D). (E.F)

И все пак всички споменати логически правила важат за горната схема.

Ако ще използвате само 5 входа от горните 6 входа И портата, можем да свържем издърпващ резистор на всеки един щифт и сега той става 5 вход И порта.

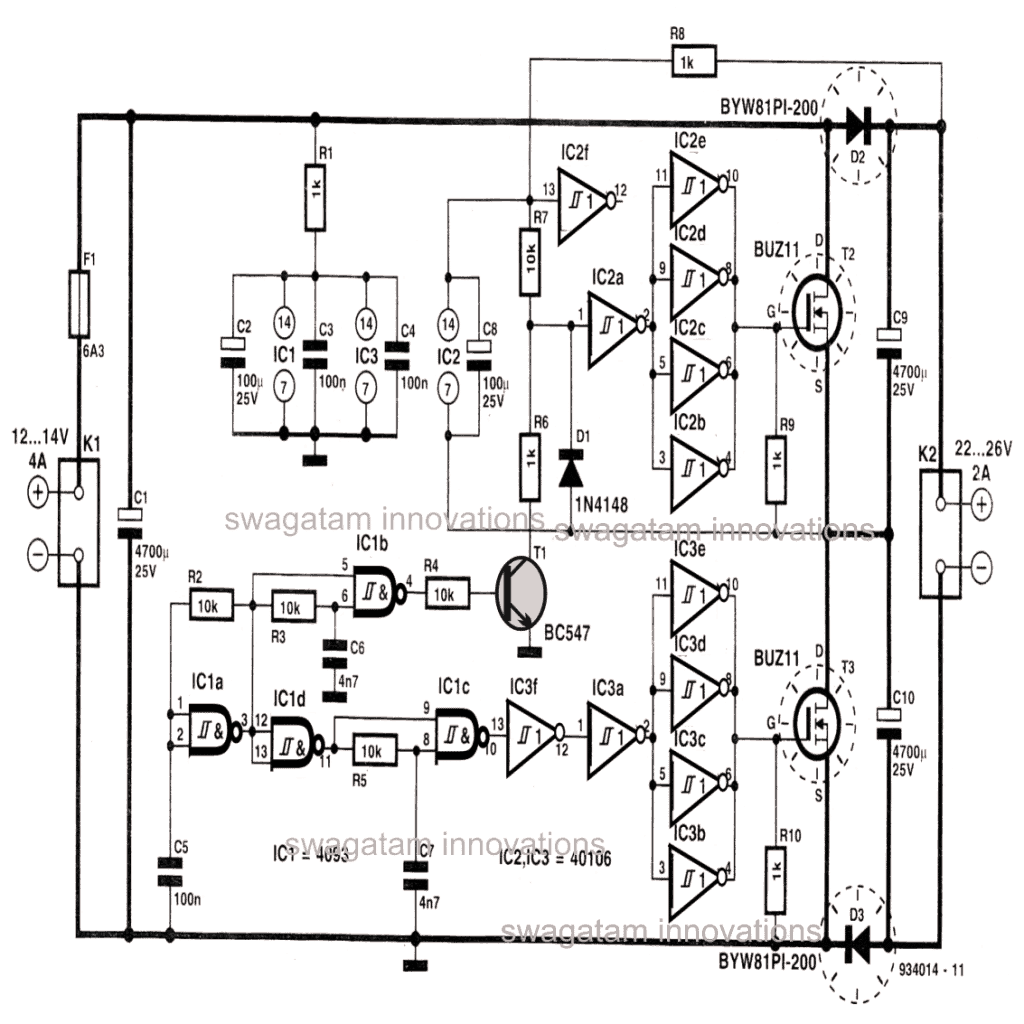

Транзистор, базиран на две входни логически и порта:

Сега знаем как функционира логика И порта, нека да конструираме 2 вход И порта, използвайки два NPN транзистора. Логическите интегрални схеми са изградени по почти същия начин.

Схема на два транзистора и порта:

На изхода „Y“ можете да свържете светодиод, ако изходът е висок, светодиодът ще свети (LED + Ve терминал на „Y“ с 330 ома резистор и отрицателен към GND).

Когато приложим висок сигнал към основата на двата транзистора, и двата транзистора се включват, + 5V сигналът ще бъде достъпен в излъчвателя на T2, като по този начин изходът става висок.

Ако някой от транзисторите е ИЗКЛЮЧЕН, няма да е налице положително напрежение в емитер на Т2, но поради 1K падащия резистор отрицателното напрежение ще бъде на разположение на изхода, така че изходът е посочен като нисък.

Сега знаете как да изградите своя логика и порта.

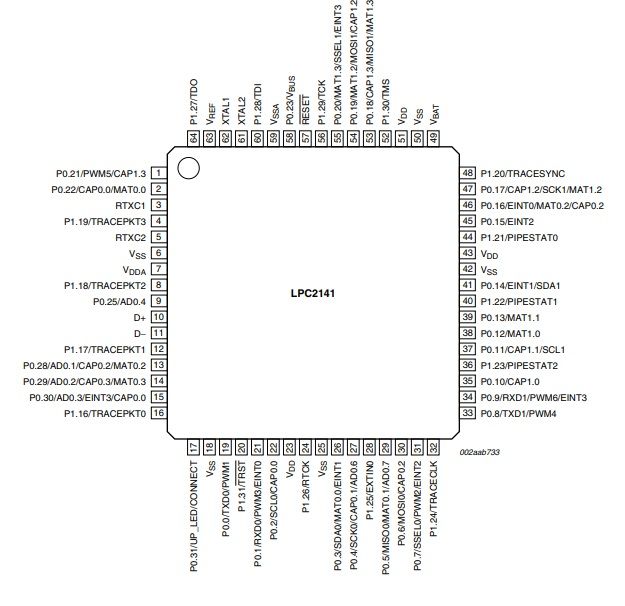

Quad AND порта IC 7408:

Ако искате да закупите логика И порта от пазара, ще получите в горната конфигурация.

Той има 14 щифта, щифт # 7 и щифт # 14 са съответно GND и Vcc. Работи при 5V.

Забавяне на разпространението:

Забавянето на разпространението е времето, необходимо на изхода да се промени от LOW на HIGH и обратно.

Забавянето на разпространението от LOW до HIGH е 27 наносекунди.

Забавянето на разпространението от HIGH до LOW е 19 наносекунди.

Други често достъпни интегрални схеми за порта „И“:

• 74LS08 Quad 2-input

• 74LS11 Тройна 3-входна

• 74LS21 Двоен 4-вход

• CD4081 Quad 2-input

• CD4073 Тройна 3-входна

• CD4082 Двоен 4-вход

Винаги можете да се обърнете към лист с данни за горните интегрални схеми за повече информация.

Колко логична е функцията на портата „Exclusive NOR“

В тази публикация ще разгледаме логическата порта „Ex-NOR” или Exclusive-NOR gate. Ще разгледаме основната дефиниция, символ, таблица на истината, еквивалентна схема Ex-NOR, реализация на Ex-NOR, използвайки логически NAND порти и накрая, ще направим общ преглед на входа Ex-OR с вход quad 2 IC 74266.

Какво представлява портата „Exclusive NOR“?

Това е електронна порта, чийто изход се превръща в „висока“ или „1“ или „вярна“ или издава „положителен сигнал“, когато входовете са четен брой логически „1s“ (или „true“ или „high“ или „ положителен сигнал ”).

Например: Кажете Exclusive NOR порта с ‘n’ брой входове, ако входовете са логически „HIGH“ с 2 или 4 или 6 входа (четен брой входове „1s“) изходът се превръща в „HIGH“.

Дори ако не прилагаме никаква логика „високо“ към входните щифтове (т.е. нулев брой логика „HIGH“ и цялата логика „LOW“), все пак „нула“ е четно число, което изходът превръща в „HIGH“.

Ако броят на приложените логически “1s” е ODD, тогава изходът се превръща в “LOW” (или “0” или “false” или “negative signal”).

Това е противоположно на логическия „Изключителен ИЛИ“ порта, където изходът му се превръща в „HIGH“, когато входовете са НЕЧЕН брой логически „1s“.

Забележка:

Понятието „Високо“, „1“, „положителен сигнал“, „вярно“ по същество е същото (Положителният сигнал е положителният сигнал на батерията или захранването).

Понятието „LOW“, „0“, „отрицателен сигнал“, „false“ по същество са еднакви (отрицателен сигнал е отрицателният сигнал на батерията или захранването).

Илюстрация на портата „Exclusive NOR“:

Ексклузивна верига за ексклузивен NOR:

Горното е еквивалентната схема за логика Ex-NOR, която по същество е комбинация от логика „Изключително ИЛИ” порта и логическа „НЕ” порта.

Тук „A“ и „B“ са двата входа и „Y“ се извежда.

Булевият израз за логически Ex-NOR порта: Y = (AB) ̅ + AB.

Ако „A“ е „1“, а „B“ е „1“, изходът е ((AB) ̅ + AB) = 0 + 1 = „1“ или „HIGH“

Ако „A“ е „0“, а „B“ е „1“, изходът е ((AB) ̅ + AB) = 0 + 0 = „0“ или „LOW“

Ако „A“ е „1“, а „B“ е „0“, изходът е ((AB) ̅ + AB) = 0 + 0 = „0“ или „LOW“

Ако „A“ е „0“, а „B“ е „0“, изходът е ((AB) ̅ + AB) = 1 + 1 = „1“ или „HIGH“

Горните условия са опростени в таблицата на истината.

Таблица на истината (два входа):

| A (вход) | B (ВХОД) | Y (изход) |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

3 Входна ексклузивна NOR порта:

Илюстрация на 3 входни Ex-NOR порта:

Таблица на истината за 3 входна логика EX-OR порта:

| A (ВХОД) | B (ВХОД) | C (ВХОД) | Y (ИЗХОД) |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

За 3-те входни Ex-NOR порта булевото уравнение става: A ̅ (BC) ̅ + ABC ̅ + AB ̅C + A ̅BC.

Логическият “Ex-NOR” портал не е фундаментален логически портал, а комбинация от различни логически портали. Портата Ex-NOR може да бъде реализирана с помощта на логически „ИЛИ“ портали, логическа „И“ порта и логическа „NAND“ порта, както следва:

Еквивалентна схема за порта “Exclusive NOR”:

Горният дизайн има основен недостатък, имаме нужда от 3 различни логически порта, за да направим една Ex-NOR порта. Но ние можем да преодолеем този проблем, като внедряваме Ex-NOR порта само с логически „NAND“ порти, това също е икономично да се измисли.

Изключителна NOR порта, използваща NAND порта:

Изключителните NOR порти се използват за изпълнение на сложни изчислителни задачи като аритметични операции, двоични суматори, двоично изваждане, проверки на четността и те се използват като цифрови компаратори.

Logic Exclusive-NOR Gate IC 74266:

Ако искате да закупите логически Ex-NOR порта от пазара, ще получите в горната DIP конфигурация.

Той има 14 щифта, щифт # 7 и щифт # 14 са съответно GND и Vcc. Работи при 5V.

Забавяне на разпространението:

Забавянето на разпространението е времето, необходимо на изхода да се промени от НИСКО на ВИСОКО и обратно след даване на вход.

Забавянето на разпространението от LOW до HIGH е 23 наносекунди.

Забавянето на разпространението от HIGH до LOW е 23 наносекунди.

Често достъпни интегрални схеми за порта 'EX-NOR':

74LS266 Quad 2-input

CD4077 Quad 2-input

Как работи NAND Gate

В обяснението по-долу ще разгледаме портата за цифрова логика NAND. Ще разгледаме основната дефиниция, символ, таблица на истината, многовходна NAND порта, ще изградим 2-входна NAND порта, базирана на транзистор, различни логически порти, използващи само NAND порта и накрая ще направим преглед на NAND порта IC 7400.

Какво е Logic “NAND” Gate?

Това е електронна порта, чийто изход се превръща в „LOW“ или „0“ или „false“ или издава „отрицателен сигнал“, когато всички входове на NAND портите са „high“ или „1“ или „true“ или „ положителен сигнал ”.

Например: Кажете NAND порта с ‘n’ брой входове, ако всички входове са „високи“, изходът се превръща в „LOW“. Дори ако един вход е „LOW“ или „0“ или „false“ или „negative signal“, изходът се превръща в „HIGH“ или „1“ или „true“ или издава „положителен сигнал“.

Забележка:

Понятието „Високо“, „1“, „положителен сигнал“, „вярно“ по същество е същото (Положителният сигнал е положителният сигнал на батерията или захранването).

Понятието „LOW“, „0“, „отрицателен сигнал“, „false“ по същество са еднакви (отрицателен сигнал е отрицателният сигнал на батерията или захранването).

Илюстрация на символа на логическия NAND порта:

Тук „A“ и „B“ са двата входа и „Y“ се извежда.

Този символ е „И“ порта с инверсия „о“.

Логическа “NAND” порта еквивалентна схема:

Логическата NAND порта е комбинацията от логическа порта „И“ и логическа порта „НЕ“.

Булевият израз за логическа NAND порта: Изходът „Y“ е допълващо умножение на двата входа „A“ и „B“. Y = ((A.B) ̅)

Булевото умножение се обозначава с точка (.), А допълващата (инверсия) е представена с лента (-) над буква.

Ако „A“ е „1“, а „B“ е „1“, изходът е ((A.B) ̅) = (1 x 1) ̅ = „0“ или „LOW“

Ако „A“ е „0“, а „B“ е „1“, изходът е ((A.B) ̅) = (0 x 1) ̅ = „1“ или „HIGH“

Ако „A“ е „1“, а „B“ е „0“, изходът е ((A.B) ̅) = (1 x 0) ̅ = „1“ или „HIGH“

Ако „A“ е „0“, а „B“ е „0“, изходът е ((A.B) ̅) = (0 x 0) ̅ = „1“ или „HIGH“

Горните условия са опростени в таблицата на истината.

Таблица на истината (два входа):

| A (вход) | B (ВХОД) | Y (изход) |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

3-входна порта „NAND“:

Илюстрация на 3 входни NAND порта:

Логическите NAND порти могат да имат „n“ брой входове, което означава, че може да има повече от два входа

(Логическите NAND порти ще имат поне два входа и винаги един изход).

За 3 входна NAND порта булевото уравнение се превръща по следния начин: ((A.B.C) ̅) = Y, подобно за 4 входни и по-горе.

Таблица на истинатаза 3 входна логическа NAND порта:

| A (ВХОД) | B (ВХОД) | C (ВХОД) | Y (ИЗХОД) |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Многовходни логически NAND порти:

Наличните в търговската мрежа Logic NAND порти се предлагат само в 2, 3 и 4 входа. Ако имаме повече от 4 входа, тогава трябва да каскадираме портите.

Например, можем да имаме четири входни логически NAND порта, като каскадираме 5 две входни NAND порта, както следва:

Сега булевото уравнение за горната схема става Y = ((A.B.C.D) ̅)

И все пак всички споменати логически правила важат за горната схема.

Ако ще използвате само 3 входа от горните 4 входа NAND порта, можем да свържем издърпващ резистор към всеки един пин и сега той става 3 вход NAND порта.

Две входни логически NAND порта, базирани на транзистор:

Сега знаем как функционира логическата NAND порта, нека конструираме 2 входна NAND порта, използвайки две

NPN транзистори. Логическите интегрални схеми са изградени по почти същия начин.

Схема на два транзисторни NAND порта:

На изхода 'Y' можете да свържете светодиод, ако изходът е висок, светодиодът ще свети (LED + Ve терминал на 'Y' с 330 ома резистор и отрицателен към GND).

Когато приложим висок сигнал към основата на двата транзистора, и двата транзистора се включват, сигналът за заземяване ще бъде достъпен в колектора на Т1, като по този начин изходът се превръща в „НИСКО“.

Ако някой от транзисторите е ИЗКЛЮЧЕН, т.е. прилагайки сигнал „LOW“ към базата, няма да има наличен заземителен сигнал в колектора на T1, но поради издърпващия резистор 1K положителният сигнал ще бъде наличен на изхода и изходът се завърта 'ВИСОКО'.

Сега знаете как да изградите логически NAND порта на собствения си.

Различни логически портали, използващи NAND порта:

Портата NAND е известна още като „универсална логическа порта“, тъй като можем да направим всяка булева логика с тази единична порта. Това е предимство за изработването на интегрални схеми с различни логически функции и изготвянето на една порта е икономично.

В горните схеми са показани само 3 вида порти, но можем да направим всякаква логическа логика.

Четириъгълна NAND порта IC 7400:

Ако искате да закупите логическа NAND порта от пазара, ще получите в горната DIP конфигурация.

Той има 14 щифта, щифт # 7 и щифт # 14 са съответно GND и Vcc. Работи при 5V.

Забавяне на разпространението:

Забавянето на разпространението е времето, необходимо на изхода да се промени от LOW на HIGH и обратно, след като даде вход.

Забавянето на разпространението от LOW до HIGH е 22 наносекунди.

Забавянето на разпространението от HIGH до LOW е 15 наносекунди.

Налични са няколко други интегрални схеми за NAND порта:

- 74LS00 Quad 2-input

- 74LS10 Тройна 3-входна

- 74LS20 Двоен 4-вход

- 74LS30 Единичен 8-вход

- CD4011 Quad 2-вход

- CD4023 Тройна 3-входна

- CD4012 Двоен 4-вход

Как работи NOR Gate

Тук ще изследваме цифровата логическа NOR порта. Ще разгледаме основната дефиниция, символ, таблица на истината, многовходна NOR порта, ще изградим базирана на транзистор 2 входна NOR порта, различни логически порти, използващи само NOR порта и накрая ще направим преглед на NOR портата IC 7402.

Какво е Logic “NOR” Gate?

Това е електронна порта, чийто изход се превръща в „HIGH“ или „1“ или „true“ или издава „положителен сигнал“, когато всички входове на NOR портите са „LOW“ или „0“ или „false“ или „ отрицателен сигнал ”.

Например: Кажете NOR порта с ‘n’ брой входове, ако всички входове са „LOW“, изходът се превръща в „HIGH“. Дори ако един вход е “HIGH” или “1” или “true” или “положителен сигнал”, изходът се превръща в “LOW” или “0” или “false” или издава “отрицателен сигнал”.

Забележка:

Понятието „Високо“, „1“, „положителен сигнал“, „вярно“ по същество е същото (Положителният сигнал е положителният сигнал на батерията или захранването).

Понятието „LOW“, „0“, „отрицателен сигнал“, „false“ по същество са еднакви (отрицателен сигнал е отрицателният сигнал на батерията или захранването).

Илюстрация на символа за логическа NOR порта:

Тук „A“ и „B“ са двата входа и „Y“ се извежда.

Този символ е „ИЛИ“ порта с инверсия „o“.

Логическа “NOR” порта еквивалентна схема:

Логическата NOR порта е комбинацията от логическа „OR“ порта и логическа „NOT“ порта.

Булевият израз за логическа NOR порта: Изходът „Y“ е допълващо добавяне на двата входа „A“ и „B“. Y = ((A + B) ̅)

Булевото добавяне се обозначава с (+), а допълващото (инверсия) е представено с лента (-) върху буква.

Ако „A“ е „1“ и „B“ е „1“, изходът е ((A + B) ̅) = (1+ 1) ̅ = „0“ или „LOW“

Ако „A“ е „0“, а „B“ е „1“, изходът е ((A + B) ̅) = (0+ 1) ̅ = „0“ или „LOW“

Ако „A“ е „1“, а „B“ е „0“, изходът е ((A + B) ̅) = (1+ 0) ̅ = „0“ или „LOW“

Ако „A“ е „0“, а „B“ е „0“, изходът е ((A + B) ̅) = (0+ 0) ̅ = „1“ или „HIGH“

Горните условия са опростени в таблицата на истината.

Таблица на истината (два входа):

| A (вход) | B (ВХОД) | Y (изход) |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

3-входна „NOR“ порта:

Илюстрация на 3 входа NOR порта:

Логическите NOR порти могат да имат ‘n’ брой входове, което означава, че могат да имат повече от два входа (Logic NOR портите ще имат поне два входа и винаги един изход).

За 3 входна NOR порта булевото уравнение се превръща по следния начин: ((A + B + C) ̅) = Y, подобно за 4 входа и по-горе.

Таблица на истината за 3 входни логически NOR порта:

| A (ВХОД) | B (ВХОД) | C (ВХОД) | Y (ИЗХОД) |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

Многовходни логически NOR порти:

Наличните в търговската мрежа Logic NOR порти се предлагат само в 2, 3 и 4 входа. Ако имаме повече от 4 входа, тогава трябва да каскадираме портите.

Например, можем да имаме четири входни логически NOR порта, като каскадираме 5 две входни NOR порта, както следва:

Сега булевото уравнение за горната схема става Y = ((A + B + C + D) ̅)

И все пак всички споменати логически правила важат за горната схема.

Ако ще използвате само 3 входа от горните 4 входа NOR порта, можем да свържем падащ резистор към всеки един от щифта и сега той става 3 вход NOR порта.

Две входни логически NOR порта, базирани на транзистор:

Сега знаем как функционира логическата NOR порта, нека да конструираме 2 входна NOR порта, използвайки два NPN транзистора. Логическите интегрални схеми са изградени по почти същия начин.

Схема на два транзисторни NOR порта:

На изхода 'Y' можете да свържете светодиод, ако изходът е висок, светодиодът ще свети (LED + Ve терминал на 'Y' с 330 ома резистор и отрицателен към GND).

Когато приложим сигнал „HIGH“ към основата на двата транзистора, и двата транзистора се включват и земният сигнал ще бъде достъпен в колектора на T1 и T2, като по този начин изходът се превръща в „LOW“.

Ако приложим “HIGH” към някой от транзисторите, все още отрицателният сигнал ще бъде наличен на изхода, което кара изхода да става “LOW”.

Ако приложим сигнал „LOW“ към основата на два транзистора, и двата се изключват, но поради издърпващия резистор изходът се превръща в „HIGH“.

Сега знаете как да изградите логическа НИ порта на собствения си.

Различни логически портали, използващи NOR порта:

ЗАБЕЛЕЖКА: NAND и NOR са двете порти, иначе известни като универсални порти.

Портата NOR също е „универсална логическа порта“, защото можем да направим всякакви логически логики с тази единична порта. Това е предимство за изготвяне на интегрални схеми с различни логически функции и изготвянето на една порта е икономично, това е същото и за NAND порта.

В горните схеми са представени само 3 типа порти, но можем да направим всякакви логически логики.

Четириъгълна NOR порта IC 7402:

Ако искате да закупите логическа NOR порта от пазара, ще получите в горната DIP конфигурация.

Той има 14 щифта, щифт # 7 и щифт # 14 са съответно GND и Vcc. Работи при 5V.

Забавяне на разпространението:

Забавянето на разпространението е времето, необходимо на изхода да се промени от LOW на HIGH и обратно, след като даде вход.

Забавянето на разпространението от LOW до HIGH е 22 наносекунди.

Забавянето на разпространението от HIGH до LOW е 15 наносекунди.

Има няколко други интегрални схеми за NOR порта:

- 74LS02 Quad 2-input

- 74LS27 Тройна 3-входна

- 74LS260 Двоен 4-вход

- CD4001 Quad 2-вход

- CD4025 Тройна 3-входна

- CD4002 Двоен 4-вход

Logic NOT Gate

В този пост ще разгледаме логиката „НЕ“ порта. Ще научим за неговата основна дефиниция, символ, таблица на истината, еквиваленти на порта NAND и NOR, инвертори на Schmitt, осмилатор на вратата NOT, НЕ порта с транзистор и накрая ще разгледаме логическия инвертор NOT gate IC 7404.

Преди да започнем да разглеждаме детайлите на логическата NOT порта, която се нарича още цифров инвертор, не трябва да се бърка с „инверторите на захранването“, които се използват в слънчеви или резервни захранвания у дома или в офиса.

Какво е Logic “NOT” Gate?

Това е единичен вход и единичен изход логическа порта, чийто изход е допълнение към входа.

Горната дефиниция гласи, че ако входът е „HIGH“ или „1“ или „true“ или „положителен сигнал“, изходът ще бъде „LOW“ или „0“ или „false“ или „отрицателен сигнал“.

Ако входът е “LOW” или “0” или “false” или “negative signal”, изходът ще бъде обърнат към “HIGH” или “1” или “true” или “положителен сигнал”

Забележка:

Понятието „Високо“, „1“, „положителен сигнал“, „вярно“ по същество е същото (Положителният сигнал е положителният сигнал на батерията или захранването).

Понятието „LOW“, „0“, „отрицателен сигнал“, „false“ по същество са еднакви (отрицателен сигнал е отрицателният сигнал на батерията или захранването).

Илюстрация на Logic NOT Gate:

Да приемем, че „A“ е входът, а „Y“ е изходът, булевото уравнение за логически NOT порта е: Ā = Y.

Уравнението гласи, че изходът е инверсия на входа.

Таблица на истината за логически НЕ порта:

| ДА СЕ (ВХОД) | Y. (ИЗХОД) |

| 0 | 1 |

| 1 | 0 |

Непортите винаги ще имат един вход (и винаги имат един изход), той се категоризира като устройства за вземане на решения. Символът „o“ на върха на триъгълника представлява допълнение или инверсия.

Този символ „o“ е не само ограничен до логическата порта „NOT“, но също така може да се използва от всякакви логически портали или всяка цифрова верига. Ако „o“ е на входа, това означава, че входът е активен-нисък.

Активно-ниско: Изходът става активен (активиране на транзистор, светодиод или реле и т.н.), когато е даден вход „LOW“.

NAND и NOR порти еквивалентни:

Портата “NOT” може да бъде конструирана с помощта на логически “NAND” и логически “NOR” портали чрез свързване на всички входни щифтове, това се отнася за порта с 3, 4 и по-високи входни щифтове.

Транзисторна логическа порта 'НЕ':

Логиката „НЕ“ може да бъде конструирана от NPN транзистор и 1K резистор. Ако приложим сигнал “HIGH” към основата на транзистора, земята се свързва към колектора на транзистора, като по този начин изходът се превръща в “LOW”.

Ако приложим сигнал „LOW“ към основата на транзистора, транзисторът остава изключен и няма да бъде свързан към земята, но изходът ще бъде изтеглен „HIGH“ от издърпващия резистор, свързан към Vcc. По този начин можем да направим логически 'НЕ' порта, използвайки транзистор.

Инвертори на Шмит:

Ще проучим тази концепция с автоматично зарядно устройство, за да обясним използването и функционирането на инверторите на Schmitt. Да вземем примера с процедурата за зареждане на литиево-йонна батерия.

Литиево-йонната батерия 3,7 V се зарежда, когато батерията достигне 3 V до 3,2 V, напрежението на батерията нараства постепенно по време на зареждане и батерията трябва да бъде прекъсната при 4,2 V. След зареждане напрежението в отворената верига на батерията пада около 4,0 V .

Сензор за напрежение измерва границата на изключване и задейства релето, за да спре зареждането. Но когато напрежението падне под 4.2V, зарядното устройство открива, че не е заредено и започва зареждането до 4.2V и прекъсва, отново напрежението на батерията пада до 4.0V и започва зареждането отново и тази лудост циклира отново и отново.

Това ще убие батерията бързо, за да преодолеем този проблем, ни е необходимо по-ниско прагово ниво или „LTV“, така че батерията да не започне да се зарежда, докато батерията падне до 3 V до 3,2 V. Горното напрежение на прага или „UTV“ е 4.2V в този пример.

Инверторът на Schmitt е направен, за да превключва изходното си състояние, когато напрежението пресича напрежението на горния праг и остава същото, докато входът достигне напрежението на долния праг.

По същия начин, след като входът премине напрежението на долния праг, изходът остава същият, докато входът достигне напрежението на горния праг.

Няма да промени състоянието си между LTV и UTV.

Сега, поради това, ВКЛ. / ИЗКЛ. Ще бъде много по-плавно и нежеланите трептения ще бъдат премахнати, а също така веригата ще бъде по-устойчива на електрически шум.

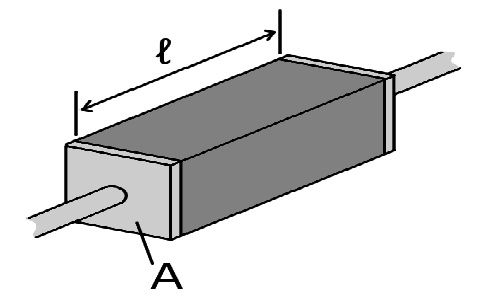

Schmitt NOT Gate Oscillator:

Горната схема е осцилатор, който произвежда квадратна вълна при 33% работен цикъл. Първоначално кондензаторът е в разредено състояние и сигналът за заземяване ще бъде достъпен на входа на портата NOT.

Изходът се превръща в положителен и зарежда кондензатора чрез резистор „R“, кондензаторът се зарежда до горното прагово напрежение на инвертора и променя състоянието, изходът превръща отрицателен сигнал и кондензаторът започва да се разрежда през резистора „R“, докато напрежението на кондензатора достигне долното ниво на прага и променя състоянието, изходът се превръща в положителен и зарежда кондензатора.

Този цикъл се повтаря, докато захранването е дадено на веригата.

Честотата на горния генератор може да бъде изчислена: F = 680 / RC

Където F е честота.

R е съпротивление в ома.

C е капацитет във фарад.

Преобразувател на квадратни вълни:

Горната схема ще преобразува синусоидалния сигнал в квадратна вълна, всъщност може да преобразува всякакви аналогови вълни в квадратна вълна.

Двата резистора R1 и R2 работят като делител на напрежението, това се използва, за да се получи точка на отклонение и кондензаторът блокира всички DC сигнали.

Ако входният сигнал надвиши горното или по-ниското ниво, изходът се превръща

LOW или HIGH според сигнала, това води до квадратна вълна.

Инвертор IC 7404 NOT gate:

IC 7404 е един от най-често използваните логически интегрални схеми. Той има 14 щифта, щифт # 7 е заземен, а щифт # 14 е Vcc. Работното напрежение е от 4.5V до 5V.

Забавяне на разпространението:

Забавянето на разпространението е времето, необходимо на портата за обработка на изхода след даване на вход.

По логика „NOT“ портата отнема около 22 нано секунди, за да промени състоянието си от HIGH на LOW и обратно.

Има няколко други логики „НЕ портални интегрални схеми:

• 74LS04 Hex Inverting NOT Gate

• 74LS14 Hex Schmitt Inverting NOT Gate

• 74LS1004 шестнадесетични инвертиращи драйвери

• CD4009 Hex Inverting NOT Gate

• CD4069 Hex Inverting NOT Gate

Как работи ИЛИ порта

Сега нека разгледаме цифровата логика ИЛИ портите. Ще разгледаме основната дефиниция, символ, таблица на истината, мулти вход ИЛИ порта, ще изградим базирана на транзистор 2 входа ИЛИ порта и накрая ще направим преглед на ИЛ порта IC 7432.

Какво е Logic “OR” Gate?

Това е електронна порта, чийто изход се превръща в „LOW“ или „0“ или „false“ или издава „отрицателен сигнал“, когато всички входове на OR портите са „LOW“ или „0“ или „false“ или „ отрицателен сигнал ”.

Например: Кажете ИЛИ порта с ‘n’ брой входове, ако всички входове са „LOW“, изходът се превръща в „LOW“. Дори ако един вход е “HIGH” или “1” или “true” или “положителен сигнал”, изходът се превръща в “HIGH” или “1” или “true” или издава “положителен сигнал”.

Забележка:

Понятието „Високо“, „1“, „положителен сигнал“, „вярно“ по същество е същото (Положителният сигнал е положителният сигнал на батерията или захранването).

Понятието „LOW“, „0“, „отрицателен сигнал“, „false“ по същество са еднакви (отрицателен сигнал е отрицателният сигнал на батерията или захранването).

Илюстрация на символа за логика ИЛИ порта:

Тук „A“ и „B“ са двата входа и „Y“ се извежда.

Булевият израз за логическа ИЛИ порта: Изходът „Y“ е добавяне на двата входа „A“ и „B“, (A + B) = Y.

Булевото добавяне се обозначава с (+)

Ако „A“ е „1“, а „B“ е „1“, изходът е (A + B) = 1 + 1 = „1“ или „висок“

Ако „A“ е „0“, а „B“ е „1“, изходът е (A + B) = 0 + 1 = „1“ или „висок“

Ако „A“ е „1“, а „B“ е „0“, изходът е (A + B) = 1 + 0 = „1“ или „висок“

Ако „A“ е „0“, а „B“ е „0“, изходът е (A + B) = 0 + 0 = „0“ или „Low“

Горните условия са опростени в таблицата на истината.

Таблица на истината (два входа):

| A (вход) | B (ВХОД) | Y (изход) |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

3-входна „ИЛИ“ порта:

Илюстрация на 3 вход ИЛИ порта:

Логическите ИЛИ порти могат да имат „n“ брой входове, което означава, че могат да имат повече от два входа (Логическите ИЛИ портите ще имат поне два входа и винаги един изход).

За логика с 3 входа ИЛИ булевото уравнение се превръща по следния начин: (A + B + C) = Y, подобно за 4 входа и по-горе.

Таблица на истината за 3 логически входа ИЛИ порта:

| A (ВХОД) | B (ВХОД) | C (ВХОД) | Y (ИЗХОД) |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

Многовходна логика ИЛИ Порти:

Наличните в търговската мрежа логически ИЛИ портали се предлагат само в 2, 3 и 4 входа. Ако имаме повече от 4 входа, тогава трябва да каскадираме портите.

Можем да имаме шест входни логически ИЛИ порта, като каскадираме 2-те входни ИЛИ порта, както следва:

Сега булевото уравнение за горната схема става Y = (A + B) + (C + D) + (E + F)

И все пак всички споменати логически правила важат за горната схема.

Ако ще използвате само 5 входа от горните 6 входа ИЛИ порта, можем да свържем падащ резистор на всеки един щифт и сега той става 5 вход ИЛИ порта.

Транзистор, базиран на две входни логически ИЛИ порта:

Сега знаем как функционира логически ИЛИ порта, нека да конструираме 2 вход ИЛИ порта, използвайки два NPN транзистора. Логическите интегрални схеми са изградени по почти същия начин.

Схема на два транзистора ИЛИ порта:

На изхода „Y“ можете да свържете светодиод, ако изходът е висок, светодиодът ще свети (LED + Ve терминал на „Y“ с 330 ома резистор и отрицателен към GND).

Когато приложим LOW сигнал към основата на двата транзистора, и двата транзистора се изключват, сигналът за заземяване ще бъде достъпен в излъчвателя на T2 / T1 чрез 1k падащ резистор, като по този начин изходът се превръща в LOW.

Ако някой от транзисторите е ВКЛЮЧЕН, положително напрежение ще бъде на разположение на излъчвателя на T2 / T1, като по този начин изходът се превръща в HIGH.

Сега знаете как да конструирате логика ИЛИ собствена порта.

Четириъгълна ИЛИ порта IC 7432:

Ако искате да закупите логическа ИЛИ порта от пазара, ще получите в горната конфигурация.

Той има 14 щифта, щифт # 7 и щифт # 14 са съответно GND и Vcc. Работи при 5V.

Забавяне на разпространението:

Забавянето на разпространението е времето, необходимо на изхода да се промени от LOW на HIGH и обратно.

Забавянето на разпространението от НИСКО до ВИСОКО е 7,4 наносекунди при 25 градуса по Целзий.

Забавянето на разпространението от HIGH до LOW е 7,7 наносекунди при 25 градуса по Целзий.

• 74LS32 Quad 2-input

• CD4071 Quad 2-input

• CD4075 Тройна 3-входна

• CD4072 Двоен 4-вход

Ексклузивна логика - ИЛИ Порта

В този пост ще разгледаме логическата XOR порта или Exclusive-OR портата. Ще разгледаме основната дефиниция, символ, таблица на истината, XOR еквивалентна схема, реализация на XOR с помощта на логически NAND порти и накрая, ще направим преглед на входа на четворка 2 Ex-OR порта IC 7486.

В предишните публикации научихме за три основни логически порта 'И', 'ИЛИ' и 'НЕ'. Също така научихме, че използвайки тези три основни порта, можем да изградим две нови логически порта „NAND“ и „NOR“.

Има още две логически порти, въпреки че тези две не са основни порти, но тя е изградена от комбинацията от другите логически порти и нейното булево уравнение е толкова жизненоважно и много полезно, че се счита за отделни логически порти.

Тези две логически порти са „Exclusive OR“ и „Exclusive NOR“. В този пост ще изследваме само логиката Exclusive OR gate.

Какво представлява портата „Exclusive OR“?

Това е електронна порта, чийто изход се превръща в „висока“ или „1“ или „вярна“ или издава „положителен сигнал“, когато двата логически входа са различни по отношение един на друг (това е приложимо само за два 2 входа Ex -ИЛИ порта).

Например: Кажете изключителна ИЛИ порта с „два“ входа, ако един от входния щифт A е „HIGH“, а входният pin B е „LOW“, тогава изходът се превръща в „HIGH“ или „1“ или „true“ или „Положителен сигнал“.

Ако и двата входа са на едно и също логическо ниво, т.е. и двата извода „HIGH“ или и двата извода „LOW“, изходът се превръща в „LOW“ или „0“ или „false“ или „отрицателен сигнал“.

Забележка:

Понятието „Високо“, „1“, „положителен сигнал“, „вярно“ по същество е същото (Положителният сигнал е положителният сигнал на батерията или захранването).

Понятието „LOW“, „0“, „отрицателен сигнал“, „false“ по същество са еднакви (отрицателен сигнал е отрицателният сигнал на батерията или захранването).

Илюстрация на Logic Exclusive OR порта:

Тук „A“ и „B“ са двата входа и „Y“ се извежда.

Булевият израз за логически Ex-OR порта: Y = (A.) ̅B + A.B ̅

Ако „A“ е „1“ и „B“ е „1“, изходът е (A ̅.B + A.B ̅) = 0 x 1 + 1 x 0 = „1“ или „LOW“

Ако „A“ е „0“ и „B“ е „1“, изходът е (A ̅.B + A.B ̅) = 1 x 1 + 0 x 0 = „1“ или „HIGH“

Ако „A“ е „1“ и „B“ е „0“, изходът е (A ̅.B + A.B ̅) = 0 x 0 + 1 x 1 = „1“ или „HIGH“

Ако „A“ е „0“ и „B“ е „0“, изходът е (A ̅.B + A.B ̅) = 1 x 0 + 0 x 1 = „0“ или „Low“

Горните условия са опростени в таблицата на истината.

Таблица на истината (два входа):

| A (вход) | B (ВХОД) | Y (изход) |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

В горните две входни логически Ex-OR порта, ако двата входа са различни, т.е. '1' и '0', изходът се превръща в 'HIGH'. Но с 3 или повече входни логики Ex-OR или като цяло изходът на Ex-OR се превръща в „HIGH“ само когато на порта е приложен ODD номерът на логиката „HIGH“.

Например: Ако имаме 3 входа Ex-OR порта, ако приложим логика “HIGH” само към един вход (нечетен брой логика “1”) изходът се превръща в “HIGH”. Ако приложим логика “HIGH” към два входа (това е четен брой логика “1”), изходът се превръща в “LOW” и т.н.

3 Входни ексклузивни ИЛИ порта:

Илюстрация на 3 вход EX-OR порта:

Таблица на истината за 3 входна логика EX-OR порта:

| A (ВХОД) | B (ВХОД) | C (ВХОД) | Y (ИЗХОД) |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

За 3 входа Ex-OR порта булевото уравнение става: A (BC) ̅ + A ̅BC ̅ + (AB) ̅C + ABC

Както описахме по-рано, логическата порта 'Ex-OR' не е основна логическа порта, а комбинация от различни логически портали. Портата Ex-OR може да бъде реализирана с помощта на логическа „OR“ порта, логическа „AND“ порта и логическа „NAND“ порта, както следва:

Еквивалентна схема за порта „Изключително ИЛИ“:

Горният дизайн има основен недостатък, имаме нужда от 3 различни логически порта, за да направим една Ex-OR порта. Но можем да преодолеем този проблем, като приложим Ex-OR порта само с логически NAND порти, това също е икономично да се измисли.

Изключителна ИЛИ порта, използваща NAND порта:

Изключителни ИЛИ порти се използват за изпълнение на сложни изчислителни задачи като аритметични операции, пълни суматори, полусумари, той също може да достави функционалност за изпълнение.

Ексклузивна логика ИЛИ Gate IC 7486:

Ако искате да закупите логическа Ex-OR порта от пазара, ще получите в горната DIP конфигурация.

Той има 14 щифта, щифт # 7 и щифт # 14 са съответно GND и Vcc. Работи при 5V.

Забавяне на разпространението:

Забавянето на разпространението е времето, необходимо на изхода да се промени от НИСКО на ВИСОКО и обратно след даване на вход.

Забавянето на разпространението от LOW до HIGH е 23 наносекунди.

Забавянето на разпространението от HIGH до LOW е 17 наносекунди.

Често достъпни интегрални схеми за порта „EX-OR“:

- 74LS86 Quad 2-input

- CD4030 Quad 2-вход

Надявам се горното подробно обяснение да ви е помогнало да разберете какво представляват логическите порти и как работят логическите порти, ако все още имате въпроси? Моля, изразете в раздела за коментари, може да получите бърз отговор.

Предишна: Тестери за изтичане на кондензатор - Намерете бързо течащи кондензатори Напред: Цифров буфер - Работен, Определение, Таблица на истината, Двойна инверсия, Вентилатор