ECL (емитерно свързана логика) е изобретен за първи път в IBM през август 1956 г. от Hannon S. Yourke. Тази логика е известна също като логика на текущия режим, използвана в компютрите на IBM 7090 и 7094. Семейството ECL е много бързо в сравнение с цифрова логика семейства. Като цяло, това логическо семейство осигурява забавяне на разпространението по-малко от 1 ns. Това е логическа фамилия, базирана на биполярни транзистори. Това е най-бързата логическа семейна схема, която е достъпна за проектиране на конвенционална логическа система. Тази статия обсъжда общ преглед на емитерна свързана логическа верига , работа с приложения.

Какво е емитерно свързана логика?

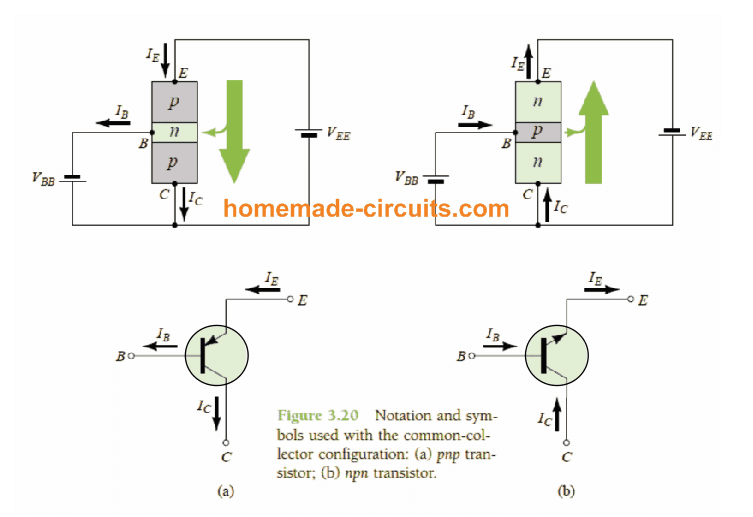

Емитер-свързаната логика е най-добрата BJT -базирана логическа фамилия, използвана в дизайна на конвенционалната логическа система. Понякога се нарича още логика на текущия режим, която е много високоскоростна цифрова технология. Като цяло, ECL се счита за най-бързата логическа интегрална схема, където постига своята високоскоростна работа чрез използване на много малко колебание на напрежението и избягване на навлизането на транзисторите в областта на насищане.

Реализацията на ECL използва положително захранващо напрежение, което е известно като PECL или ECL с положителна референция. В ранните ECL вентили се използва захранване с отрицателно напрежение поради устойчивостта на шум. След това положително реферираният ECL стана много известен поради своите по-съвместими логически нива в сравнение с TTL логическите семейства.

Емитер-свързаната логика разсейва огромно количество статична мощност, но общата консумация на ток е ниска в сравнение с CMOS при високи честоти. И така, ECL е от полза главно във вериги за разпределение на часовника и приложения, базирани на висока честота.

Емитерно свързани логически характеристики

Характеристиките на ECL ще ги направят използвани в много приложения, базирани на висока производителност.

- ECL предоставя два изхода, които винаги се допълват един друг, тъй като работата на веригата се основава на диференциален усилвател.

- Това логическо семейство е подходящо главно за методи за монолитно производство, тъй като логическите нива са функция на съотношенията на резистора.

- Устройствата от семейството ECL генерират правилния и допълнителен изход на предложената функция, без да използват външни инвертори. Следователно, това намалява броя на пакетите и изискванията за захранване и също така намалява проблемите, възникващи от времеви закъснения.

- ECL устройствата в дизайна на диференциален усилвател предлагат широка гъвкавост на работата, така че ECL схемите позволяват да бъдат използвани както като цифрови, така и като линейни вериги.

- Дизайнът на ECL gate обикновено има висок и нисък входен импеданс, което е изключително благоприятно за постигане на голямо разпръскване, както и способност за задвижване.

- ECL устройствата генерират постоянен ток на захранването, за да опростят дизайна на захранването.

- Устройствата на ECL, включващи изходи с отворен емитер, просто им позволяват да включат капацитет на задвижване на преносна линия.

Емитерно свързана логическа верига

Емитерно-свързаната логическа схема за инвертора е показана по-долу, която е проектирана с резистори и транзистори. В тази схема емитерните клеми на два транзистора са просто свързани към ограничаващо тока съпротивление RE, което се използва, за да се избегне навлизането на транзистора в състояние на насищане. Тук изходът на транзистора се взема от колекторния терминал вместо от емитерния терминал. Тази схема осигурява два изхода Vout (инвертиращ изход) и Vout2 (неинвертиращ изход) и входния терминал като Vin, където се дава висок или нисък вход. +Vcc = 5V.

Как работи логиката, свързана с емитер?

Работата на логиката, свързана с емитер, е, че всеки път, когато входът HIGH е подаден към веригата ECL, тогава той ще направи транзистора „Q1“ ВКЛЮЧЕН и транзистора Q2 ИЗКЛЮЧЕН, но транзисторът Q1 не е наситен. Така че това ще изтегли изхода VOUT2 до ВИСОКО и стойността на изхода VOUT1 ще бъде НИСКО поради спада в R1.

По същия начин, когато стойността на VIN, дадена на ECL, е НИСКА, тогава това ще направи транзистора Q1 ИЗКЛЮЧЕН и транзисторът Q2 ВКЛЮЧЕН. Така транзисторът Q2 няма да премине в състояние на насищане. Така че изходът VOUT1 ще бъде изтеглен от ВИСОКА стойност, а изходната стойност VOUT2 ще бъде ниска поради спада в съпротивлението на R2.

Нека видим как транзисторите Q1 и Q2 се включват и изключват, когато се приложи напрежение.

Двата транзистора като Q1 и Q2 в тази схема са свързани като диференциален усилвател чрез общ емитер резистор.

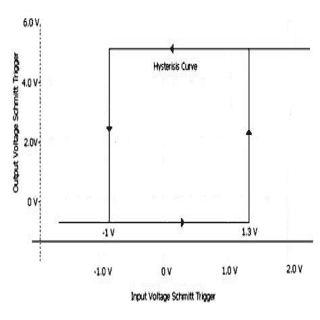

Захранващото напрежение за тази примерна верига е VCC = 5.0, VBB = 4.0 & VEE = 0 V. Стойностите на входно ниво HIGH & LOW са просто дефинирани като 4.4 V & 3.6V. Всъщност тази верига генерира НИСКИ изходни и ВИСОКИ нива, които са с 0,6 волта по-високи; това обаче се коригира в реални ECL вериги.

След като Vin е ВИСОКО, тогава транзисторът Q1 е включен, но не е наситен и транзисторът Q2 е изключен. И така, изходното напрежение като VOUT2 се изтегля до 5 V през резистора R2 и може да се покаже, че спадът на напрежението през резистора R1 е около 0,8 V, така че VOUT1 = 4,2 V (НИСКО). В допълнение VE = VOUT1 – VQ1 => 4.2V – 0.4V = 3.8V, тъй като транзистор Q1 е включен напълно.

След като Vin е НИСКО, транзисторът Q2 ще бъде включен, но не наситен и транзисторът Q1 е изключен. Следователно VOUT1 се изтегля до 5,0 V с помощта на резистор R1 и може да се покаже, че VOUT2 е 4,2 V. Също така VE => VOUT2 – VQ2 => 4,2V – 0,8V => 3,4V, тъй като транзисторът Q2 е включен.

В ECL двата транзистора никога не са в насищане като t колебанията на входното/изходното напрежение са сравнително малки като 0.8v и входният импеданс е висок, а изходното съпротивление е ниско. Това помага на ECL да работи по-бързо с по-малко време на забавяне на разпространението.

Верига с два входа, свързана с емитер, ИЛИ/НЕ

Веригата на две входни емитери, свързана с логика ИЛИ/НЕ, е показана по-долу. Тази схема е проектирана чрез модифициране на горната инверторна верига. Модификацията е чрез добавяне на допълнителен транзистор от страната на входа.

Работата на тази верига е много проста. Когато входовете, приложени към транзисторите Q1 и Q2, са ниски, тогава изходът1 (Vout1) ще стане ВИСОКА стойност. И така, този Vout1 съответства на изхода на портата NOR.

Едновременно с това, ако транзисторът Q3 е включен, тогава вторият изход (Vout2) ще бъде ВИСОК. И така, този изход Vou2 съответства на изхода на OR gate.

По същия начин, ако входовете на двата транзистора Q1 и Q2 са ВИСОКИ, тогава той ще включи транзисторите Q1 и Q2 и ще осигури нисък изход на терминала VOUT1.

Ако транзисторът Q3 е изключен по време на тази операция, тогава той ще осигури висока мощност на терминала VOUT2. И така, таблицата на истината за ИЛИ/НИТО врата е дадена по-долу.

|

Входове |

Входове | ИЛИ |

НИТО |

|

А |

б | Y | Y |

|

0 |

0 | 0 | 1 |

|

0 |

1 | 1 |

0 |

| 1 | 0 | 1 |

0 |

| 1 | 1 | 1 |

0 |

Емитерно-свързани логически характеристики

Характеристиките на ECL включват следното.

- В сравнение с TTL, ECL има по-бързо време на разпространение, вариращо от 0,5 до 2 ns. Но разсейването на логическата мощност, свързана с емитер, е по-високо в сравнение с TTL като 30 mW.

- Входно-изходните напрежения на ECL имат малка промяна като 0,8.

- Входният импеданс на ECL е висок и изходното съпротивление е ниско; следователно транзисторът променя своите състояния много бързо.

- Капацитетът на ECLs fan-out е висок, а закъсненията на вратата са ниски.

- O/p логиката на ECL се променя от LOW към HIGH състояние, но нивата на напрежение за тези състояния ще варират между TTL и EC.

- Шумоустойчивостта на ECL е 0,4V.

Предимства и недостатъци

The предимства на емитер-свързаната логика са обсъдени по-долу.

- Fanout на ECL е 25, което е по-добро в сравнение с TTL и е ниско в сравнение с CMOS.

- Средното време на забавяне на разпространението на ECL е 1 до 4 ns, което е по-добро в сравнение с CMOS и

- TTL. Затова се нарича най-бързото логическо семейство.

- Когато BJT в емитер са свързани логически порти работят в активния регион, тогава те имат максимална скорост в сравнение с всички логически семейства.

- ECL портовете генерират допълнителни изходи.

- В захранващите кабели няма пикове на превключване на тока.

- Изходите могат да бъдат свързани съвместно, за да осигурят функцията кабелно ИЛИ.

- Параметрите на ECL не се променят много в зависимост от температурата.

- Нето на функциите, достъпни само от един чип, е голям.

The недостатъци на емитер-свързаната логика са обсъдени по-долу.

- Той има изключително по-ниска граница на шум, т.е. ±200 mV.

- Разсейването на мощността е високо в сравнение с други логически порти.

- За взаимодействие с други логически фамилии са необходими превключватели на ниво.

- Fanout ограничава капацитивното натоварване.

- В сравнение с TTL , портите ECL са скъпи.

- В сравнение с CMOS и TTL, шумоустойчивостта ECL е най-лоша.

Приложения

Приложенията на емитер-свързаната логика включват следното.

- Свързаната с емитер логика се използва като логика и интерфейсна технология в изключително високоскоростни комуникационни устройства като интерфейси за оптични предаватели, Ethernet и ATM (режим на асинхронен трансфер) мрежи.

- ECL е логическа фамилия, базирана на BJT, където нейната високоскоростна работа може да бъде постигната чрез използване на сравнително малко колебание на напрежението и избягване на преминаването на транзисторите в областта на насищане.

- ECL се използва при създаването на ASLT вериги в рамките на IBM 360/91.

- ECL избягва използването на подредени транзистори, като използва еднопостово отклонение i/p и положителна обратна връзка между първични и вторични транзистори за постигане на инверторна функция.

- ECL се използва в изключително високоскоростна електроника.

По този начин, това е преглед на емитерна свързана логика или ECL – верига, работа, характеристики, характеристики и приложения. ECL е най-бързата логическа фамилия, базирана на BJT в сравнение с други цифрови логически фамилии. Той постига своята максимална скорост на работа, като използва малко колебание на напрежението и избягва преминаването на транзисторите в областта на насищане. Тази логическа фамилия осигурява невероятно забавяне на разпространението от 1ns, а в най-новите фамилии ECL това забавяне е намалено. Ето един въпрос към вас, какво е алтернативно име за ECL?