Като цяло пълният изваждащ елемент е един от най-използваните и основни комбинационни логически схеми . Това е основно електронно устройство, използвано за извършване на изваждане на две двоични числа. В по-ранната статия вече дадохме основната теория на половин суматор и пълен суматор който използва двоичните цифри за изчислението. По същия начин пълният извадител използва двоични цифри като 0,1 за изваждане. Веригата на това може да бъде изградена с логически портали като OR, Ex-OR, NAND gate. Входовете на този извадител са A, B, Bin, а изходите са D, Bout.

Тази статия дава идея за теория с пълен субтрактор, която включва предпоставките като това, което е субтрактор, дизайн с логически порти, таблица на истината и др. Тази статия е полезна за студенти по инженерство, които могат да преминат през тези теми в практическата лаборатория на HDL.

Какво е изваждач?

Изваждането на двоичните цифри може да се извърши с помощта на веригата на изваждащия. Това е един вид комбинационна логическа схема, използвана за извършване на изваждането на две двоични цифри като 0s и 1s. Изваждането на двоични цифри от 0 до 0 или 0 до 1 не променя резултата, изваждането на 1 до 1 ще доведе до 0, но изваждането на 1 до 0 се нуждае от заем.

Например, двубитовата схема за изваждане включва два входа като A & B, докато изходите са разлика и заемат. Тази верига може да бъде изградена с суматори заедно с инвертори, които са разположени сред всеки вход за данни, както и заем (Bin) вход на по-ранната фаза на FA.

Изваждащите средства се класифицират в два типа като половин изваждащ и пълен изваждащ. Тук обсъждаме пълния извадител.

Какво е пълен извадител?

Това е електронно устройство или логическа схема който извършва изваждане на две двоични цифри. Това е комбинационна логическа схема, използвана в цифровата електроника. Много комбинационни схеми се предлагат в технология с интегрални схеми а именно суматори, енкодери, декодери и мултиплексори. В тази статия ще обсъдим нейната конструкция с помощта на половината изваждащ, както и термините като таблицата на истината.

Пълен извадител

Проектирането на това може да бъде направено от два половин изваждащи, което включва три входа, като минус, изваждане и заем, заем, бит сред входовете се получава от изваждането на две двоични цифри и се изважда от следващата двойка от по-висок ред на битове, изходи като разлика и заем.

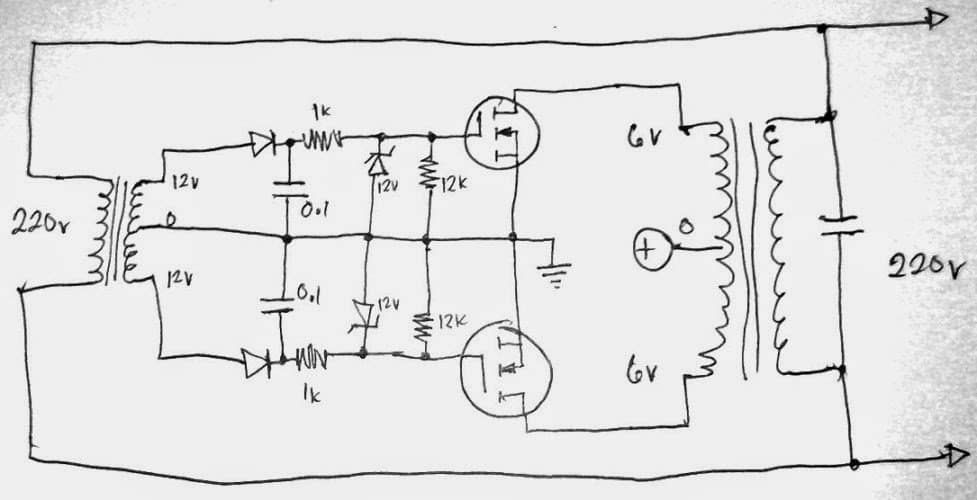

The пълна блок-схема на извадител е показано по-долу. Най-големият недостатък на половината извадител е, че не можем да направим малко заем в този изваждач. Докато в неговия дизайн всъщност можем да направим бит за заемане във веригата и да извадим с останалите два i / ps. Тук A е минута, B е изваждане и Bin е заем. Изходите са Difference (Diff) & Bout (Borrow out). Пълната схема на извадител може да се получи, като се използват две половинки изваждачи с допълнителен ИЛИ вход.

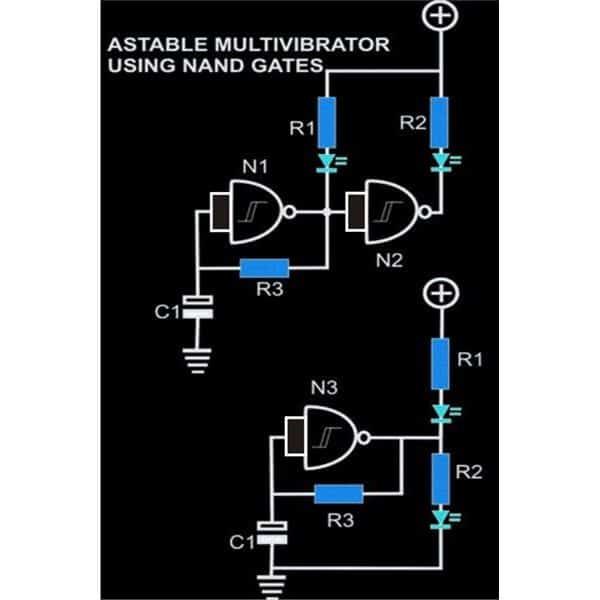

Пълна схема на извадител с логически портали

The електрическа схема на пълния извадител, използвайки основната порта s е показано на следващата блок-схема. Тази схема може да бъде направена с две вериги с половин изваждане.

В първоначалната верига на полу-Subtractor, двоичните входове са A и B. Както обсъдихме в предишната статия на полу-Subtractor, тя ще генерира два изхода, а именно разлика (Diff) и заем.

Пълен извадител, използващ Logic Gates

Разликата o / p на левия извадител се дава на веригата на лявата половина на изваждащия. По-нататък се осигурява диференциран изход към входа на дясната половина верига на Извадител Предложихме Вземете назаем в другия i / p на следващия половин верига на извадител . Още веднъж ще даде Diff, както и Borrow out the bit. Крайният изход на този извадител е Diff-output.

От друга страна, Заемът от двете половини вериги за изваждане е свързан към логическа порта ИЛИ. По-късно от даването на логика ИЛИ за два изходни бита на изваждащия, ние придобиваме окончателното заемане от изваждащия. Последният заем, който означава MSB (най-значимият бит).

Ако наблюдаваме вътрешната верига на това, можем да видим два Half Subtractor с NAND порта и XOR порта с допълнителна ИЛИ порта.

Пълна таблица на истината за изваждане

Това схема на извадител изпълнява изваждане между два бита, което има 3 входа (A, B и Bin) и два изхода (D и Bout). Тук входовете посочват minuend, subtrahend и предишен заем, докато двата изхода се означават като o / p и разлика като заем. Следващото изображение показва таблицата на истината на пълния изваждащ елемент.

Входове | Изходи | |||

Меню (A) | Изваждане (B) | Вземете назаем (кошче) | Разлика (D) | Вземете назаем (двубой) |

0 | 0 | 0 | 0 | 0 |

0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

1 | 1 | 0 | 0 | 0 |

1 | 1 | 1 | 1 | 1 |

K-Map

Опростяването на пълен извадител K-карта за горната разлика и заем е показано по-долу.

Уравненията за разликата, както и Bin, са посочени по-долу.

Изразът за разликата е,

D = A’B’Bin + AB’Bin ’+ A’BBin’ + ABBin

Изразът за Заем е,

Пояснение = A’Bin + A’B + BBin

Каскадиране на пълната схема на извадител

Преди това обсъждахме общ преглед на това като конструкция, електрическа схема с логически порти. Но ако искаме да извадим две иначе повече 1-битови числа, тази схема за изваждане е много полезна за каскадно единично битово число и също изважда повече от две двоични числа. В такива случаи се използва каскадна верига с пълен суматор с помощта на логическа порта НЕ. Преобразуването на веригата от пълен суматор в пълен извадител може да се извърши с помощта на техниката на комплемента на 2.

Обикновено инвертирайте входовете за изваждане за пълния суматор, като използвате НЕ порта, в противен случай инвертор. Чрез добавяне на този Minuend (неинвертиран вход) и Subtrahend (инвертиран вход), LSB (носещ вход) на FA веригата е 1, което означава Logic High, в противен случай изваждаме две двоични цифри, използвайки техниката на комплемента на 2. Изходът на FA е Diff bit и ако обърнем изпълнението, тогава можем да получим MSB иначе Borrow bit. Всъщност можем да проектираме веригата така, че да може да се наблюдава изхода.

Verilog код

За кодиращата част, първо, трябва да проверим структурния начин на моделиране на логическата схема. Логическата диаграма на това може да бъде изградена с помощта на AND порта, половин изваждащи вериги и комбинацията от логически портали като AND, OR, NOT, XOR gate. Както при структурното моделиране, ние обясняваме различни модули за всяко основно елементарно подреждане. В следващия код могат да бъдат дефинирани различни модули за всяка порта.

Този модул е за ИЛИ порта.

ВХОД: a0, b0

ИЗХОД: c0

И накрая, ще обединим тези модули, прецизни на портата, в единствен модул. За това тук използваме инстанция на модул. Сега тази инстанция може да се използва, след като искаме да репликираме точен модул или функция за различни набори от входни данни. Първо, ние проектираме половин извадител, след което този модул се използва за реализиране на пълен изваждащ. За изпълнението на това използваме OR порта, за да комбинираме o / ps за променливата на Bout. The Verilog код за пълния извадител е показано по-долу

модул or_gate (a0, b0, c0)

вход a0, b0

изход c0

задайте c0 = a0 | b0

краен модул

модул xor_gate (a1, b1, c1)

вход a1, b1

изход c1

задайте c1 = a1 ^ b1

краен модул

модул and_gate (a2, b2, c2)

вход a2, b2

изход c2

задайте c2 = a2 & b2

краен модул

модул not_gate (a3, b3)

вход a3

изход b3

задайте b3 = ~ a3

краен модул

module half_subtractor(a4, b4, c4, d4)

input a4, b4

изход c4, d4

тел x

xor_gate u1(a4, b4, c4)

and_gate u2 (x, b4, d4)

not_gate u3 (a4, x)

краен модул

модул full_subtractor (A, B, Bin, D, Bout)

вход A, B, Bin

изход D, бой

тел p, q, r

половин_извличател u4 (A, B, p, q)

половината_извличател u5 (p, Bin, D, r)

or_gate u6 (q, r, бой)

краен модул

Пълен извадител, използващ 4X1 мултиплексор

Изпълнението на изваждането може да се извърши чрез метода на комплемента на двамата. По този начин ние се нуждаем от използване на 1-XOR порта, който се използва за инвертиране на 1-битов и включване на такъв в битов пренос. Изходът на DIFFERENCE е подобен на изхода SUM в пълната верига на суматора, но BARROW o / p не е подобен на изхода на пълния суматор, но е обърнат, както и допълнен, като A - B = A + (-B) = A + two допълнение на B.

Дизайнът на този мултиплексор 4X1 е показан на следващата логическа схема. Този дизайн може да се направи, като се използват следните стъпки.

4X1 мултиплексор

- В стъпка 1 има два изхода като Sub и Borrow. Така че трябва да изберем 2 мултиплексора.

- В стъпка 2 таблицата на истината може да бъде приложена заедно с K-карти

- В стъпка 3 двете променливи могат да бъдат избрани като избраната от вас линия. Например B & C са в този случай.

Таблица на истината

The таблица на истината на пълен изваждащ схема, използваща 4X1 мултиплексор, включва следното

ДА СЕ | Б. | ° С | Под | Взимам на заем |

0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

1 | 1 | 1 | 1 | 1 |

Пълен извадител, използващ декодер

Проектирането на пълен извадител с помощта на 3-8 декодера може да се извърши, като се използват активни ниски изходи. Да приемем, че декодерът функционира, като използва следната логическа диаграма. Декодерът включва три входа в 3-8 декодера. Въз основа на таблицата на истината можем да напишем minterms за резултатите от разликата и заема.

От горната таблица на истината,

За различните функции в таблицата на истината, minterms могат да бъдат записани като 1,2,4,7, и по подобен начин, за заема, minterms могат да бъдат написани като 1,2,3,7. Декодерите 3-8 включват три входа, както и 8 изхода lik0 до 7 числа.

Декодер от 3 до 8

Ако входът на извадителя е 000, тогава изходът „0“ ще бъде активен, а ако входът е 001, тогава изходът „1“ ще бъде активен.

Сега изходите на извадителя могат да бъдат взети от 1, 2, 4 и 7, за да го свържете към NAND порта, тогава изходът ще бъде разликата. Тези изходи могат да бъдат свързани към други логически порти на NAND, където изходът се променя към заема.

Например, ако входът е 001, тогава изходът ще бъде 1, което означава, че е активен. Така че изходът е активен нисък и изходът може да бъде получен от NAND порта, наречена функция за разлика като висока и функцията за заем също се променя като висока. Следователно получаваме предпочитания изход. И така, накрая, декодерът работи като пълен извадител.

Предимства и недостатъци

The предимства на изваждащия включват следното.

- Проектирането на субтрактор е много просто, както и изпълнение

- Намаляване на мощността в DSP (цифрова обработка на сигнала)

- Изчислителните задачи могат да се изпълняват с висока скорост.

The недостатъци на извадителя включват следното.

- В половината извадител няма условие да се приеме подобен на заем вход от по-ранната фаза.

- Скоростта на извадителя може да бъде частична поради закъснението във веригата.

Приложения

Някои от приложения на пълен изваждащ включват следното

- Те обикновено се използват за ALU (аритметична логическа единица) в компютрите, за да се извадят като CPU и GPU за приложенията на графиката, за да се намали трудността на веригата.

- Извадителите се използват най-вече за извършване на аритметични функции като изваждане, както в електронни калкулатори, така и в цифрови устройства.

- Те са приложими и за различни микроконтролери за аритметично изваждане, таймери и брояч на програми (компютър)

- Извадителите се използват в процесорите за изчисляване на таблици, адреси и т.н.

- Също така е полезно за DSP и мрежови системи.

- Те се използват главно за ALU в компютри за изваждане като CPU и GPU за графични приложения, за да се намали сложността на веригата.

- Те се използват главно за извършване на аритметични функции като изваждане в рамките на цифрови устройства, калкулатори и др.

- Тези изваждащи устройства са подходящи и за различни микроконтролери за таймери, компютър (брояч на програми) и аритметично изваждане

- Те се използват за процесори за изчисляване на адреси, таблици и т.н.

- Внедряването на това с логически порти като NAND & NOR може да се направи с всяка пълна логическа схема на извадител, тъй като и двете порти NOR & NAND се наричат универсални порти.

От горната информация, чрез оценка на сумиращия, пълен изваждащ с помощта на две половини вериги на изваждащия и неговите таблични форми, може да се забележи, че Dout в пълния изваждащ е точно подобен на Sout на пълния сумиращ. Единствената вариация е, че A (входна променлива) се допълва в пълния извадител. По този начин е възможно да се промени веригата на пълен суматор в пълен извадител, като просто се допълни i / p A, преди да се даде на логическите порти за генериране на последния изходен бит (Bout).

Чрез използване на пълна логическа схема на извадител може да се приложи пълен извадител, използващ NAND порти и пълен изваждащ, използващ нито порти, тъй като и NAND и NOR портите се третират като универсални порти. Ето въпрос към вас, каква е разликата между половината изваждащ и пълния изваждащ?