Процесорът MicroBlaze е разработен през 2002 г., за да интегрира няколко сложни функции, за да отговори на новото, както и на нарастващото пазарно търсене. И така, процесорът MicroBlaze е основен елемент в портфолиото от нисък клас на Xilinx, за да позволи по-бързо развитие на системата, която съдържа Artix®-7 FPGA , Spartan®-6, Zynq®-7000 AP SoC. Този процесор е изключително конфигурируем, така че може да се използва като вграден процесор или микроконтролер в рамките на FPGA и също така да се използва като копроцесор в Zynq-7000 AP SoC, базирани на ARM Cortex-A9. Тази статия дава кратка информация за Процесор MicroBlaze – архитектура и работа с приложения.

Какво е процесор Microblaze?

Софтуерният микропроцесор, който е предназначен главно за FPGA на Xilinx, е известен като процесор MicroBlaze. Този процесор е просто внедрен в паметта с общо предназначение и логическата структура на FPGA на Xilinx. Този процесор е подобен на DLX архитектурата, базирана на RISC, и има гъвкава система за свързване, така че да поддържа различни вградени приложения. Основната I/O шина и AXI връзката на MicroBlaze е транзакционна шина с карта на паметта с възможност за главен-подчинен.

MicroBlaze използва специална LMB шина за достъп до локалната памет и осигурява бързо съхранение в чипа. Много части от този процесор могат да бъдат конфигурирани от потребителя като размера на кеша, дълбочината на блока за управление на паметта на тръбопровода, вградените периферни устройства и шинните интерфейси.

Характеристики на Microblaze

The характеристики на Microblaz e включват следното. Разполага с 32 регистъра с общо предназначение.

- Има 32-битови думи с инструкции, включително 2 режима на адресиране и 3 операнда.

- Адресната шина е 32-битова.

- Има 3-степенен тръбопровод или 5-степенен тръбопровод.

- Блок ALU с превключвател.

- Архитектурата на Харвард включва 32-битови данни и адресна шина.

- Интерфейс за данни & LMB или инструкция за шина на локалната памет.

- Интерфейси за поток AX14 и AX14.

- Блок с плаваща запетая и модул за управление на паметта.

- Поддържа lockstep.

- Интерфейс за отстраняване на грешки и проследяване.

Архитектура на Microbaze

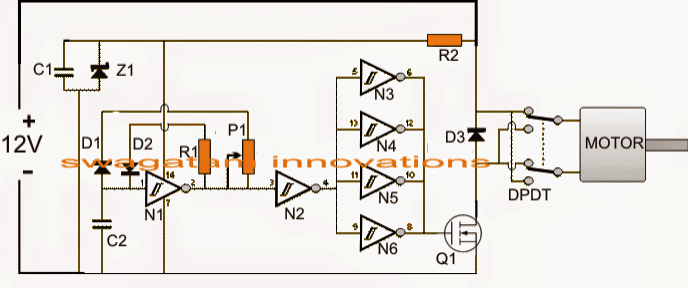

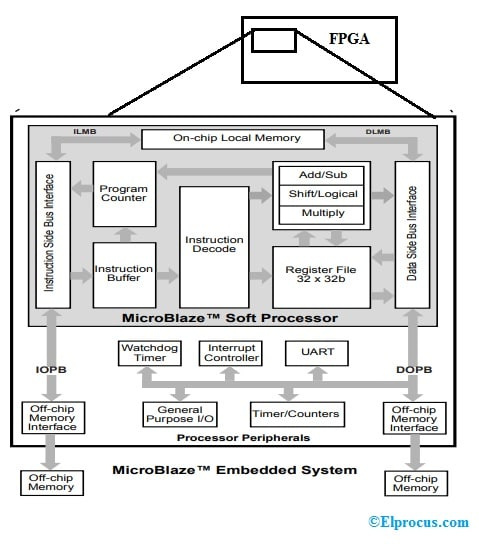

Блоковата схема на процесора MicroBlaze е показана по-долу. Този процесор MicroBlaze е изключително персонализиран и поддържа над 70 опции за дизайн. Тази архитектура показва постоянни хардуерни функции, както и конфигурируеми опции като кеш за инструкции или данни, модул за управление на паметта, модул с плаваща запетая и др.

Ан вградена система сглобен около процесор MicroBlaze, включва главно MicroBlaze Soft Processor Core, локална памет на чип, свързване на стандартна шина и периферни устройства OPB (периферна шина на чип). Процесорната система MicroBlaze варира главно от процесорно ядро от локална памет до голяма система, включваща няколко MicroBlaze процесори , външна памет и много OPB периферни устройства.

Софт процесорно ядро

Софтуерното процесорно ядро на MicroBlaze е централно за вградената система MicroBlaze. Това е много бърз и ефективен 32-битов RISC процесор, който има следните характеристики.

- Наборът от инструкции е ортогонален.

- Отделни шини за данни и инструкции.

- 32-битови регистри с общо предназначение.

- Той има допълнителен пълен 32-битов барел превключвател.

- Вградени интерфейси към бърза OCM или памет на чип и индустриалния стандарт на IBM OPB (периферна шина на чип).

Реализациите в рамките на Virtex-II и следващите устройства поддържат множество хардуери.

Локална памет на чипа

Синхронната памет е локална памет, която се използва главно за разрешаване на блокова RAM на чипа.

Стандартни шинни връзки

Интерфейсите на шините от страната на инструкциите и данните включват интерфейс към локалната памет, който се нарича LMB (Local Memory Bus) и интерфейс към периферната шина на IBM в чипа. Така че можем да проектираме системи, които стриктно се придържат към архитектурата на Харвард, в противен случай, за споделяне на ресурси, можем да използваме един OPB в комбинация чрез арбитър на шина.

Локалната шина на паметта осигурява сигурен вход от един цикъл за блокова RAM на чипа. Това е много ефективен, прост протокол за шина с един главен и е идеален за свързване на бърза локална памет. OPB или On-chip Peripheral Bus е 32-битова широка мулти-главна шина, която е идеална за обединяване на периферни устройства и външна памет към ядрото на процесора MicroBlaze.

Вградени периферни шинни периферни устройства

Хардуерната система MicroBlaze се допълва от OPB периферни устройства, за да осигури различни функции като Watchdog Timer или Timebase, Timer с общо предназначение или броячи, IC (Interrupt Controller), различни контролери като SRAM, Flash Memory, ZBT Memory, BRAM, DDR, SDRAM, UART Lite , SPI, I2C, I/O с общо предназначение, UART 16450/550 и Ethernet 10/100 MAC. Освен това можем също така да добавяме и дефинираме периферни устройства главно за персонализирани функции, в противен случай интерфейс към дизайн, който съществува в FPGA.

Комплект инструкции за Microblaze

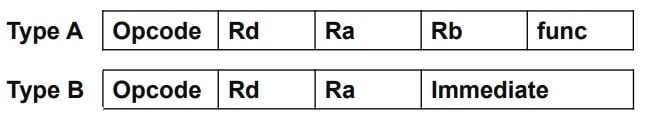

Наборите от инструкции на Microblaze са аритметика, логика, разклоняване, зареждане/съхранение и други. Размерът на всички инструкции е фиксиран. Най-много 3-регистъра могат да бъдат дадени като операнди. Microblaze включва два формата на инструкции тип A и тип B, които са показани по-долу.

Форматът на инструкции тип A се използва главно за инструкции регистър-регистр. Така че включва кода на операцията, единична дестинация и два регистъра източник. Форматът на инструкции от тип B се използва главно за инструкции за незабавно регистриране, които включват кода на операцията, единствената дестинация и единичните регистри на източника. & 16-битов източник на непосредствена стойност.

В горните два формата на инструкции кодът на операция е код на операция, Rd е регистър на местоназначение, който е кодиран с 5 бита, Ra & Rb са регистри източник, където всеки е кодиран с 5 бита, а Immediate е 16-битова стойност.

Аритметични инструкции

Аритметичните инструкции от тип A и тип B са дадени по-долу.

Тип А

|

ДОБАВЕТЕ Rd, Ra, Rb добавете |

Rd = Ra+Rb, флагът за носене е засегнат |

|

ДОБАВЕТЕ K Rd, Ra, Rb Добавете и продължете да носите |

Rd = Ra+Rb, флагът за носене не е засегнат |

| RSUB Rd, Ra, Rb Обратно изваждане |

Rd = R-Rb, флагът за носене не е засегнат |

Тип Б

|

ДОБАВИ I Rd, Ra, Imm добавете незабавно |

Rd = Ra+signExtend32 (Imm) |

|

ДОБАВИ IK Rd, Ra, Imm добавете незабавно и продължете да носите |

Rd = Ra+ signExtend32 (Imm) |

| RSUBIK Rd, Ra, Imm обратно изваждане с незабавно |

Rd = Ra+ signExtend32 (Imm) -Ra |

| SRA Rd, Ra аритметично изместване надясно |

Rd = (Ra>>1) |

Логически инструкции

Логическите инструкции тип A и тип B са дадени по-долу.

Тип А

|

ИЛИ Rd, Ra, Rb Логично или |

Rd = Ra| Rb |

|

И Rd, Ra, Rb Логична добавка |

Rd = Ra & Rb |

| XOR Rd, Ra, Rb Логотичен xor |

Rd = Rb ^ Rb |

| ANDN Rd, Ra, Rb Логично и не |

Rd = Ra & (Rb) |

Тип Б

|

ORI Rd, Ra, Imm логическо ИЛИ с незабавно |

Rd = Ra | signExtend32 (Imm) |

| ANDI Rd, Ra, Imm логическо И с незабавно |

Rd = Ra & signExtend32 (Imm) |

| XORI Rd, Ra, Imm логическо XOR с незабавно |

Rd = Ra ^ signExtend32 (Imm) |

| ANDNI Rd, Ra, Imm Логично А НЕ с незабавно |

Rd = Ra & (signExtend32 (Imm)) |

Инструкции за клонове - безусловни

Променете регистъра на програмния брояч

| BRID Imm клон незабавно с незабавно забавяне |

PC = PC+ signExtend32 (Imm) позволява изпълнение на отложен слот |

| BRLID Rd, Imm клон и връзка незабавно с незабавно забавяне (извикване на функция) |

Rd = PC PC = PC+& signExtend32 (Imm) позволява изпълнение на отложен слот |

| RTSD Ra, Imm връщане от подпрограма |

PC = Ra + signExtend32 (Imm) позволява изпълнение на отложен слот |

| RTID Ra, Imm връщане от прекъсване |

PC = Ra + signExtend32 (Imm) позволява изпълнение на отложен слот задайте разрешение за прекъсване в MSR |

Инструкции за клонове - безусловни1

Променете регистъра на програмния брояч, когато дадено условие е изпълнено

| BEQI Ra, Imm клон, ако е равен |

PC = PC+ signExtend32 (Imm) Ако Ra = = 0 |

| MASH Ra, Imm разклонение, ако не е равно |

Rd = PC PC = PC+& signExtend32 (Imm) Ако Ра! = 0 |

Инструкции за клонове - безусловни 2

Променете регистъра на програмния брояч, когато дадено условие е изпълнено

| BLTI Ra, Imm клон, ако е по-нисък от |

PC = PC+ signExtend32 (Imm) Ако Ra < 0 |

| BLEI Ra, Imm разклонение, ако по-ниско е равно на |

Rd = PC PC = PC+& signExtend32 (Imm) Ако Ra!< = 0 |

| BGTI Ra, Imm клон, ако е по-голям от |

PC = PC+ signExtend32 (Imm) Ако Ra!> 0 |

| BGEI Ra, Imm разклонение ако е по-голямо равно на |

PC = PC+signExtend32 (Imm) Ако Ra!>= 0 |

Инструкции за зареждане/съхраняване - тип A

| LW Rd, Ra, Rb Зареди дума |

Адрес = Ra+Rb Rd = *Адрес |

| SW Rd, Ra, Rb Съхранявайте дума |

Адрес – Ra+Rb *Адрес = Rd |

Тип Б

| LWI Rd, Ra, Imn Заредете дума незабавно |

Адрес = Ra + signExtend32 (Imm) Rd = *Адрес |

| SW Rd, Ra, Imm Съхранявайте думата незабавно |

Адрес = Ra + signExtend32 (Imm) *Адрес = Rd |

Други инструкции

| IMM, Imm незабавно |

Разширете Imm на предходна инструкция тип B до 32 бита. |

| MFS Rd, Sa Преместване от регистър със специално предназначение |

Rd = Sa Sa- регистър със специално предназначение, операнд източник

|

| MTS Sd, Ra Преместване в регистър със специално предназначение |

Sd = Ra Sd – регистър със специално предназначение, дестинационен операнд |

Регистри

Архитектурата на процесора MicroBlaze е напълно ортогонална, която включва 32-битови регистри с общо предназначение и 32-битови регистри със специално предназначение като програмен брояч и регистър за състоянието на машината.

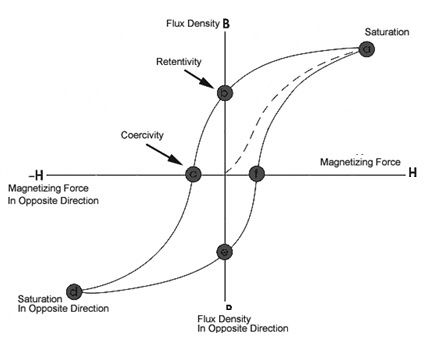

Архитектура на тръбопровода

MicroBlaze използва 3-степенна тръбопроводна архитектура, включително извличане, декодиране и завършване на етапи. Автоматично препращането на данни, разклоненията и спирането на тръбопровода се определят в рамките на хардуера.

Архитектура за зареждане или съхранение

MicroBlaze поддържа памет в три размера на данните 8 бита (байт), 16 бита (полуслова) и 32 бита (дума). Така че достъпът до памет винаги е съобразен с размера на данните. Това е Big-Endian процесор, който използва адреса на Big-Endian адреса, както и конвенции за етикетиране след достъп до паметта.

Прекъсва

След като се осъществи прекъсване, този процесор ще прекрати текущото изпълнение, за да управлява заявката за прекъсване чрез разклоняване към адрес на вектор за прекъсване и да съхрани адреса на инструкцията, която трябва да бъде изпълнена. Този процесор ще спре бъдещи прекъсвания чрез изчистване на флага IE (Разрешаване на прекъсване) в MSR (Регистър за състоянието на машината).

Как действа Microblaze?

Процесорът MicroBlaze поддържа 32-битова широчина на шината и това ядро на процесора е RISC-базиран двигател, който включва регистърен файл, базиран на 32-битова LUT RAM чрез отделни инструкции за памет и достъп до данни.

Този процесор просто поддържа както BlockRAM в чипа, така и външна памет. Подобно на IBM PowerPC; всички периферни устройства използват подобна шина CoreConnect OPB; периферните устройства на процесора са добре съчетани с PowerPC на Virtex-II Pro.

Процесорът MicroBlaze осигурява пълна гъвкавост за избор на комбинация от памет, периферни и интерфейсни функции, които ще ви осигурят прецизната система, от която се нуждаете, на единична FPGA с по-малко разходи.

Разлика Ч/Б Microblaze срещу Risc-V

The разлика между MicroBlaze и RISC v включват следното.

|

Microblaze |

Риск-V |

| Това е меко микропроцесорно ядро, предназначено главно за Xilinx FPGA.

|

RISC-V е архитектура на набор от инструкции, вкоренена в принципите на RISC.

|

| Използва RISC архитектура на Харвард. | Той използва архитектура на набор от инструкции. |

| Лицензът му е патентован (Xilinx) | Лицензът му е с отворен код. |

| Дълбочината на тръбопровода е 3 или 5. | Дълбочината на тръбопровода е 5. |

| Производителността му е 280 DMIP. | Производителността му е 250 DMIP. |

| Скоростта му е 235 MHz. | Скоростта му е 250 MHz. |

| Има 1027 LUT. | Има 4125 LUT. |

| Използваната технология е Xilinx FPGA. | Използваната технология е FPGA/ASIC. |

Предимства на Microblaze

The предимства на MicroBlaze включват следното.

- Икономичен е.

- Той е силно конфигурируем.

- Производителността му е висока в сравнение с ARM.

- Поддържа се от вграден комплект за разработка.

- Това е мек микропроцесор сърцевина.

- За да ви помогне бързо да подредите вашето приложение, този процесор включва три фиксирани конфигурации, които са свързани с добре познати процесорни класове микроконтролер, процесор за реално време и процесор за приложения.

Приложения на Microblaze

The приложения на MicroBlaze включват следното.

- Този процесор отговаря на много различни изисквания за приложения като индустриални, автомобилни, медицински и потребителски и др.

- Приложенията на MicroBlaze варират от прости автомати, базирани на софтуер, до сложни контролери, използвани във вградени приложения или интернет базирани устройства.

- Той е оптимизиран за вградени приложения като индустриален контрол, офис автоматизация и автомобили.

- MicroBlaze е в състояние да комуникира с голям набор от периферни устройства, за да се побере в приложения със среден мащаб.

- Мекият характер на този процесор го прави персонализиран за различни приложения, където дизайнерите могат да обменят функции за размер, за да отговорят на целите за цена и производителност за медицински, автомобилни, индустриални и защитни приложения.

И така, това е всичко преглед на Microblaze процесор. Това е пълнофункционално 32-битово програмируемо RISC процесорно ядро. Този процесор отговаря на различни изисквания в различни области като потребителски, медицински, индустриални, автомобилни и пазари на комуникационна инфраструктура. Той е изключително конфигурируем, така че се използва като вграден процесор или микроконтролер в рамките на FPGA, иначе като копроцесор за ARM. Ето един въпрос за вас, какво е FPGA?